热搜关键词: PCIe高速数据采集卡RFSOC高速数据采集软件无线电平台VPX高速数据采集卡高速信号采集卡PCIe数据采集数字信号处理

✕

当今高速AD采样频率单片可达几个G,这样高的采样频率一般是通过多个AD CORE并行分时采集实现的,如此一来,单通道AD采样率也可上GHz。但是面对这种情况,FPGA时钟的采样点很难定位到数据的中心稳定部分,而可能正好处于采样的AD变化区域,并且AD芯片多跟数据线到达FPGA的延迟会有不等的值。这跟AD数据线分配在同一BANK还是同时分在不同的BANK上有关,一般分在相同的BANK上并且通过手动布局可以使数据线相互之间的延迟差异很小。

因此,AD数据经过FPGA端口后首先要进行IODELAY的调整,使AD数据线对齐,即保证FPGA时钟上升沿定位到AD数据线的中心,也保证后续数据处理能够提供准确的数据。

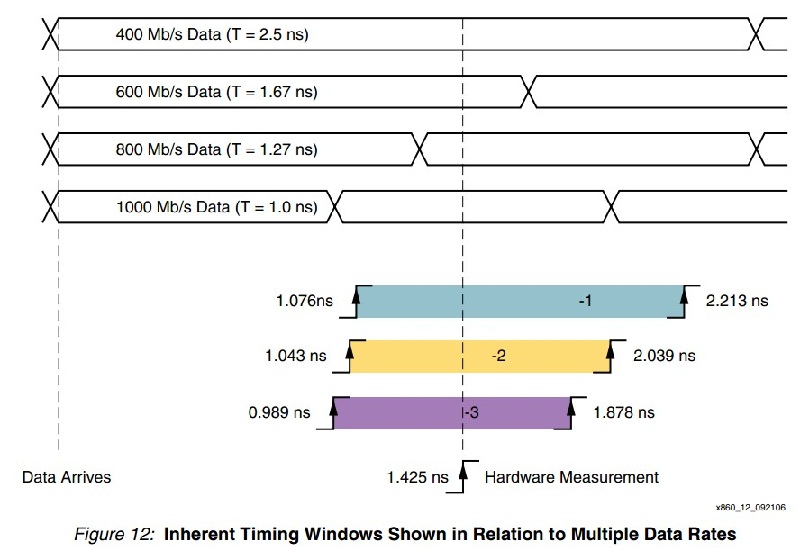

下图为不同频率下,数据线与时钟线的相对延迟。可见,在数据线速率达到800MB/s时,时钟的采样数据与真实数据已经差了一个周期。

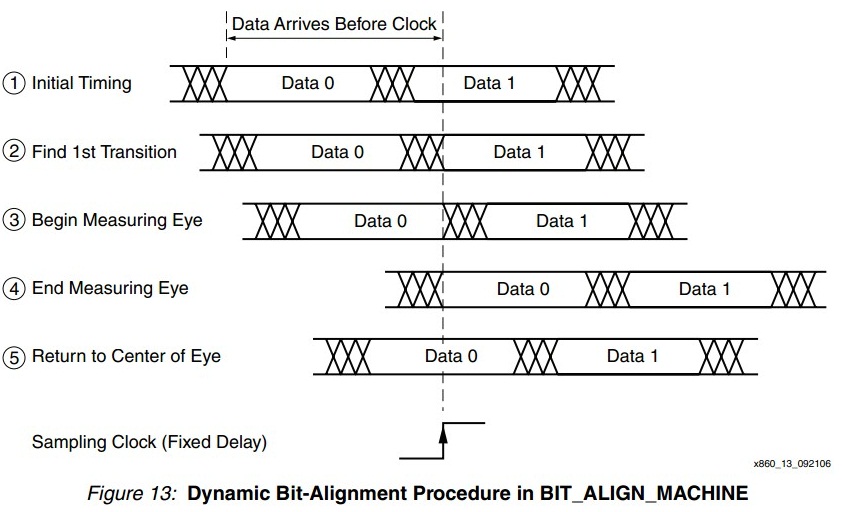

下图为IODELAY调节流程及流程图:

首先,进行位调节,其次,进行字调节。

更多关于高速数据采集产品设计的中IOdelay问题,欢迎您进一步探讨交流。

坤驰科技,为实现“专业的高速数据采集厂商”而与您共同努力!

关于坤驰科技:

坤驰科技是专注于高速数据采集与信号处理、高速数据存储与记录的高科技公司。坤驰科技为用户提供成熟的标准高速数据采集产品与技术,也可为用户提供定制化的高速信号采集解决方案。目前坤驰科技服务过的研究所、科研单位已达近百家。高速数据采集产品线涵盖PCIe、cPCI、PXIe、VPX、USB等总线,包含高速AD、DA平台、FPGA、DSP处理平台,SATA/SSD、Flash存储平台等。

全国咨询电话:400-000-4026

公司官方网站:http://www.queentest.cn

官方微博:http://e.weibo.com/queentest

官方微信:queentest或扫描: