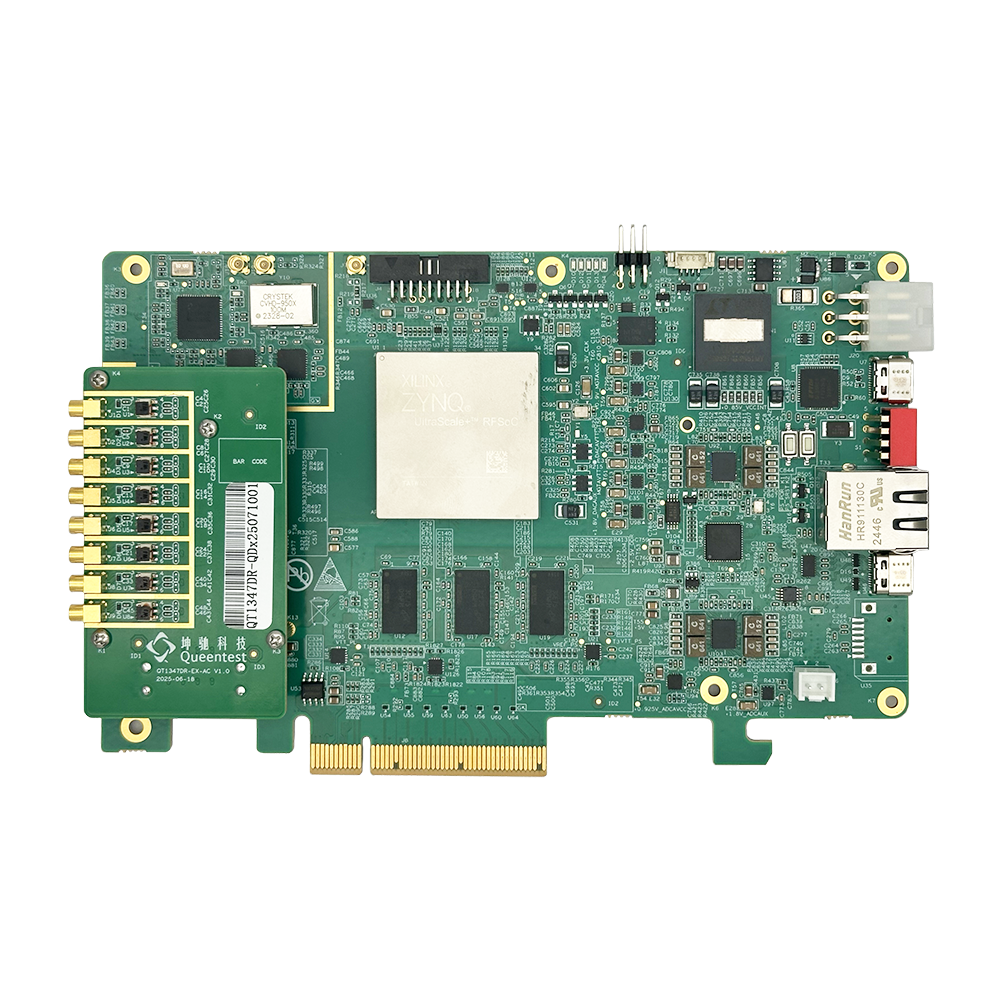

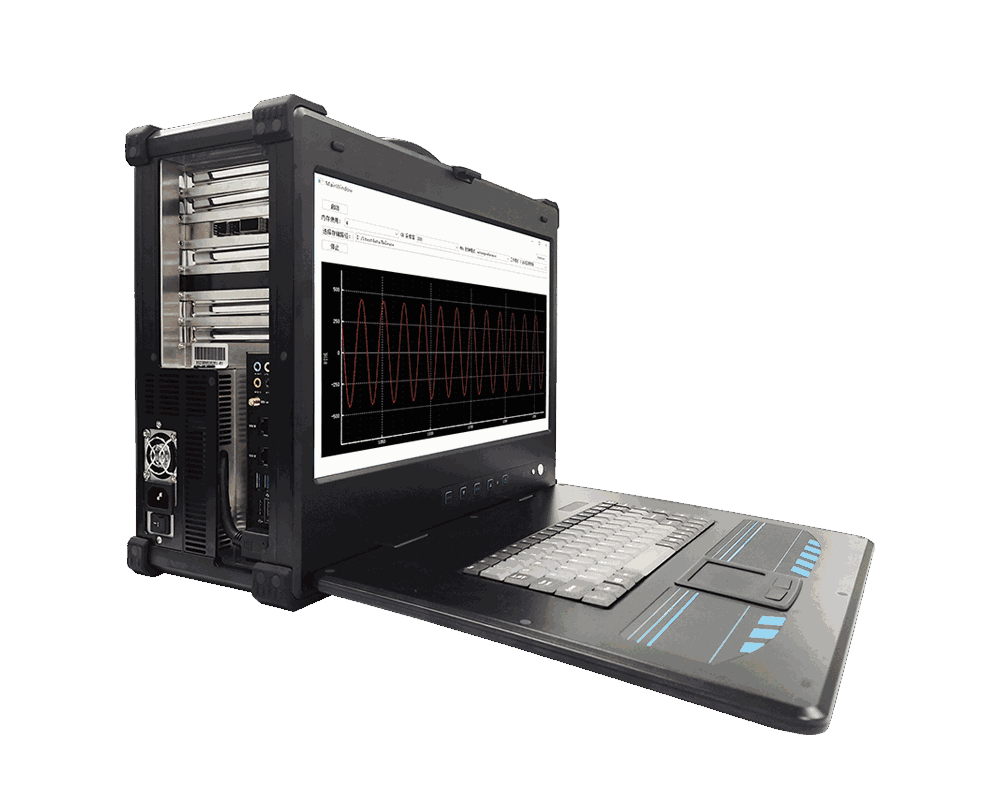

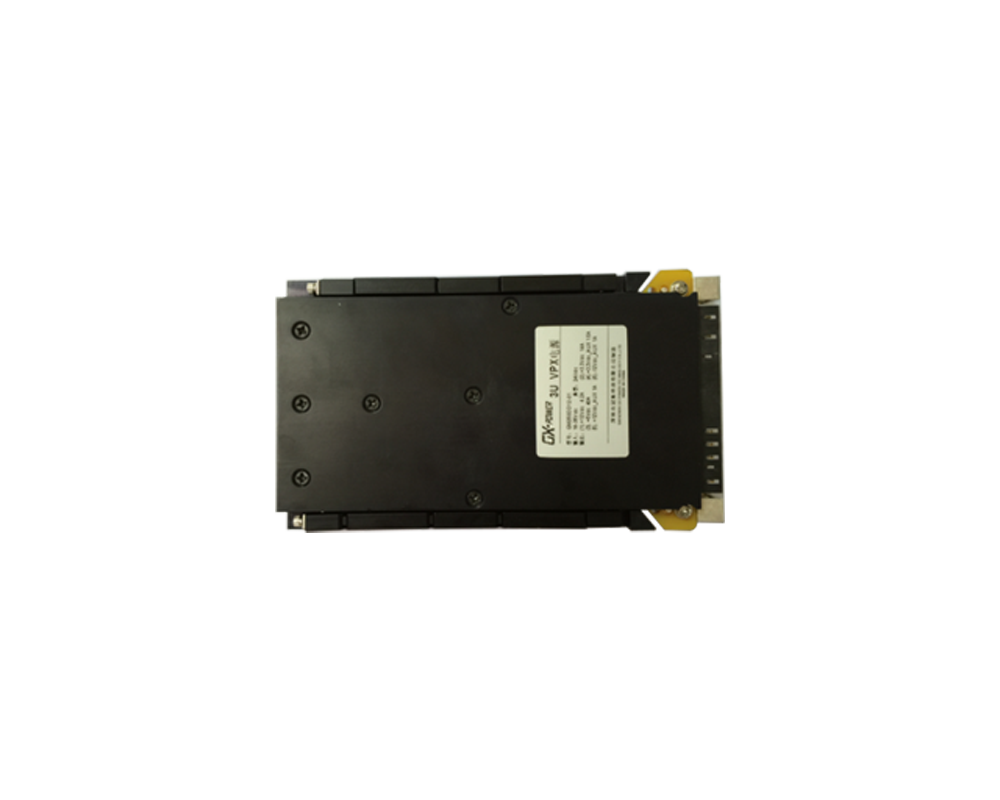

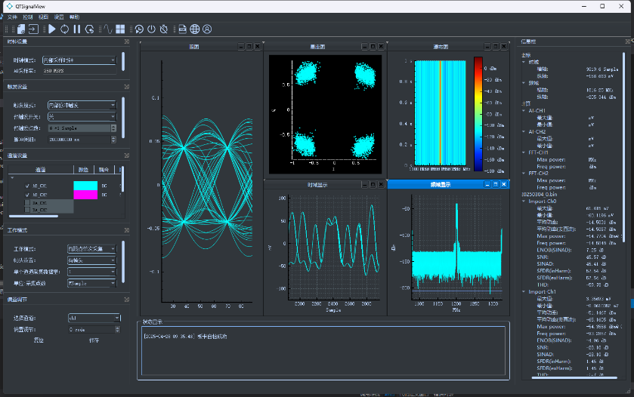

6通道400MSPS 14bit采集系统

采集系统规格:

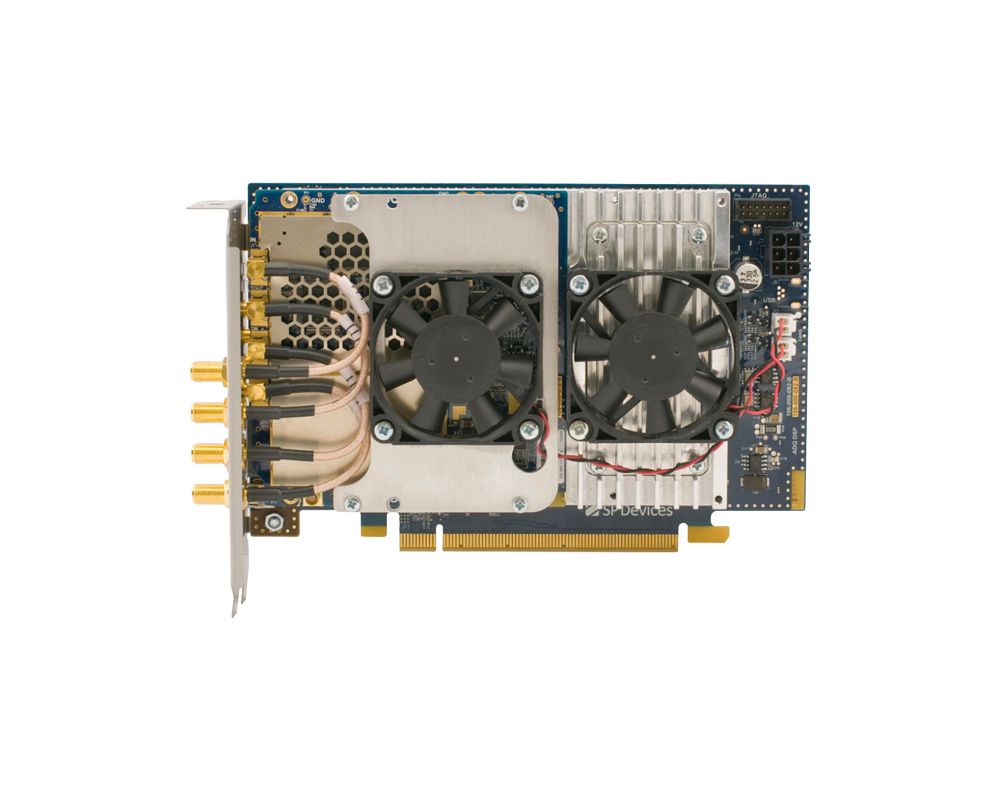

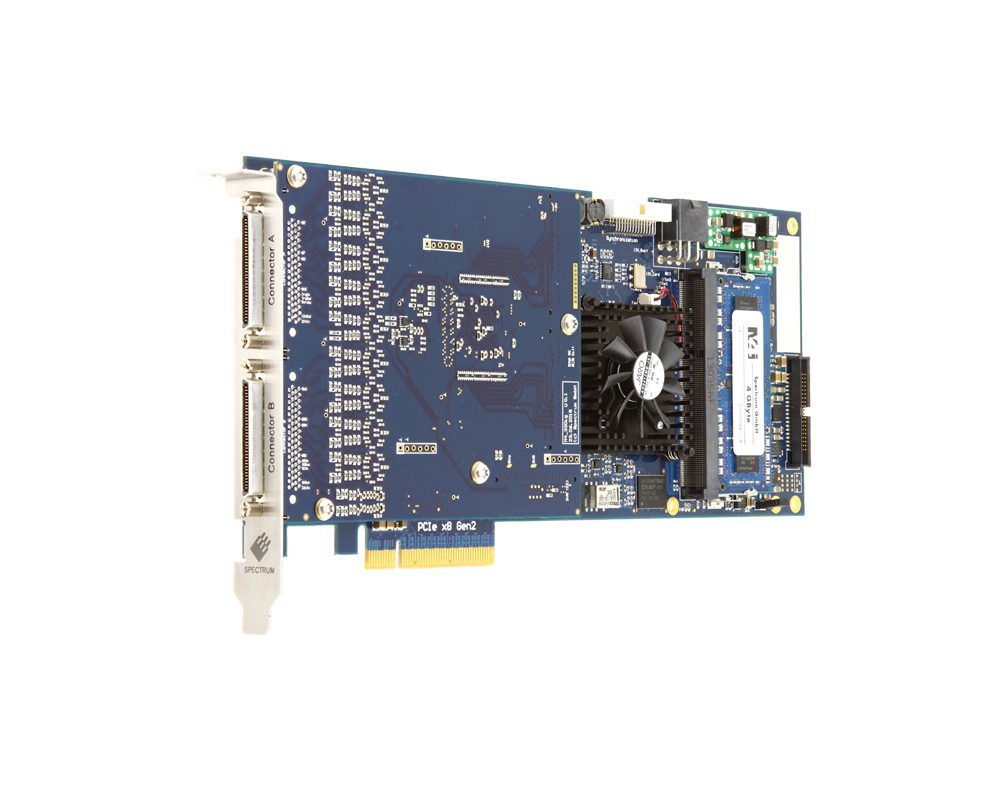

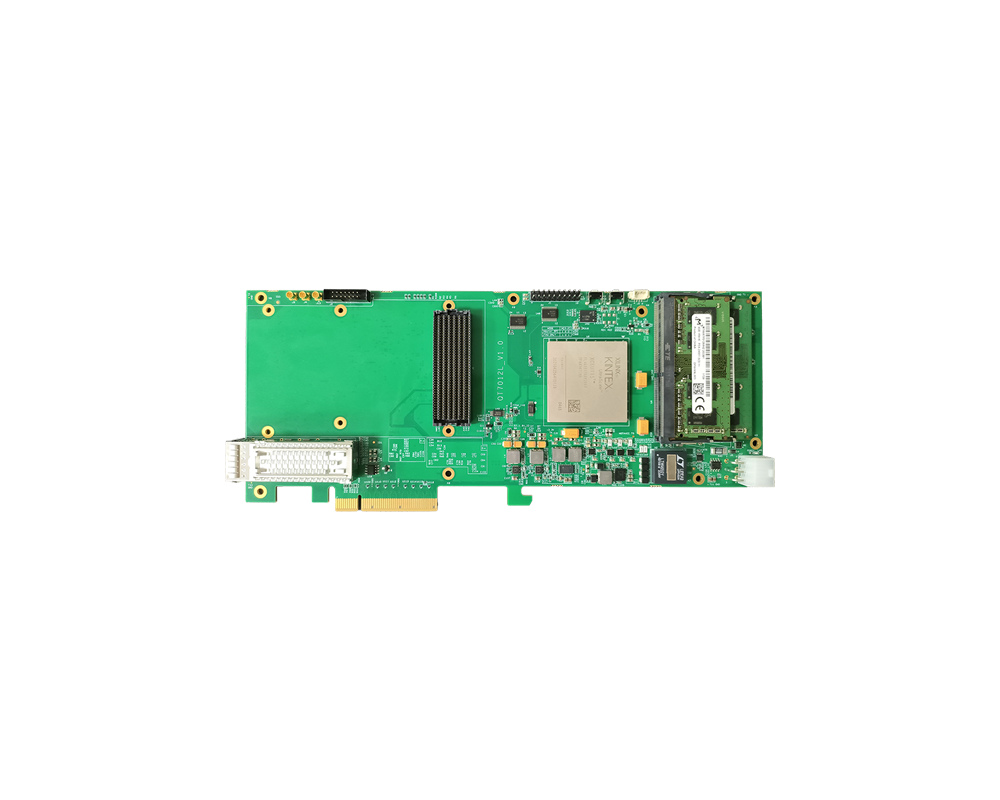

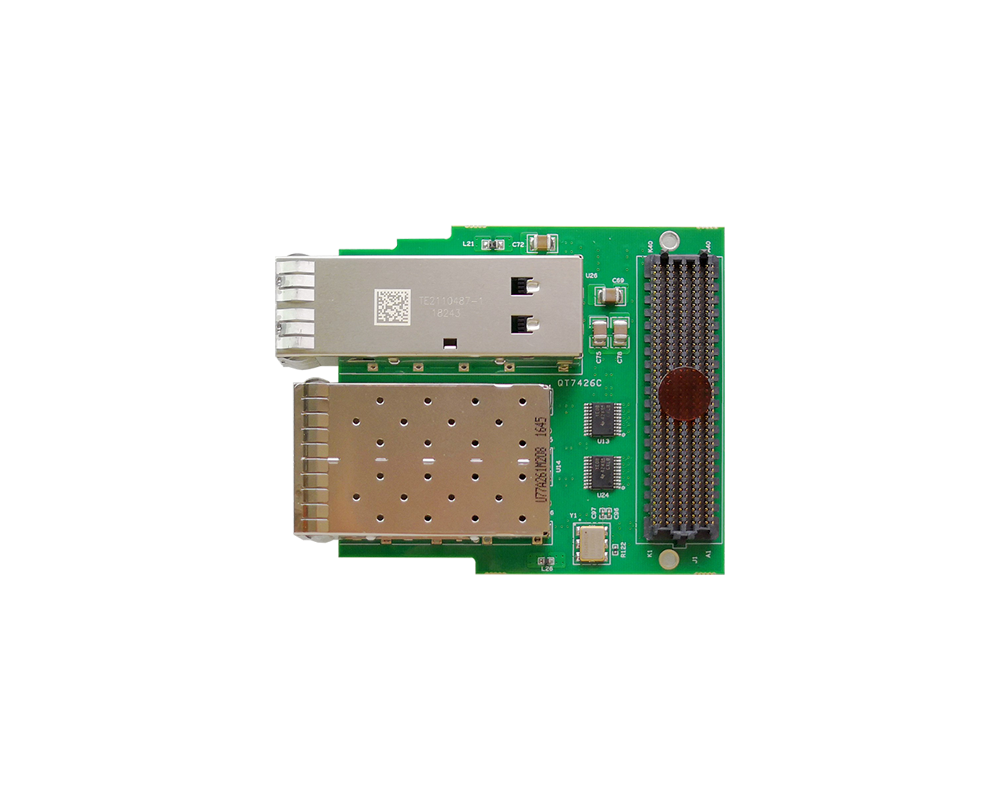

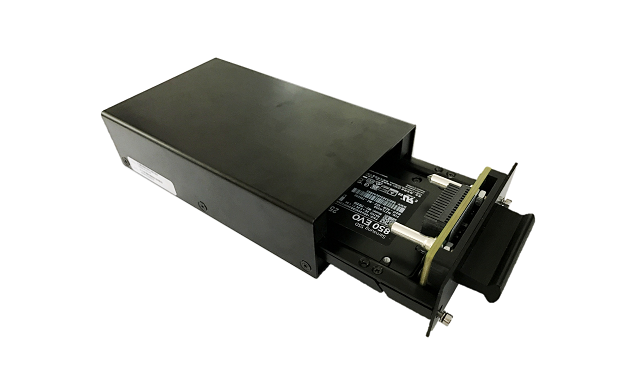

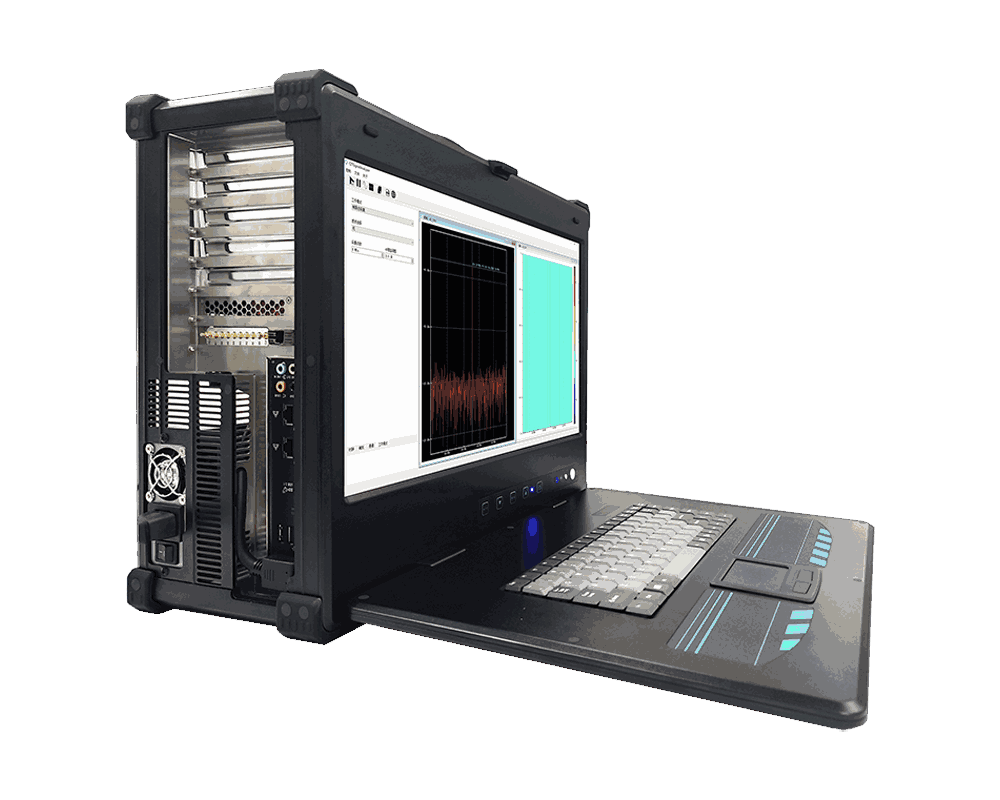

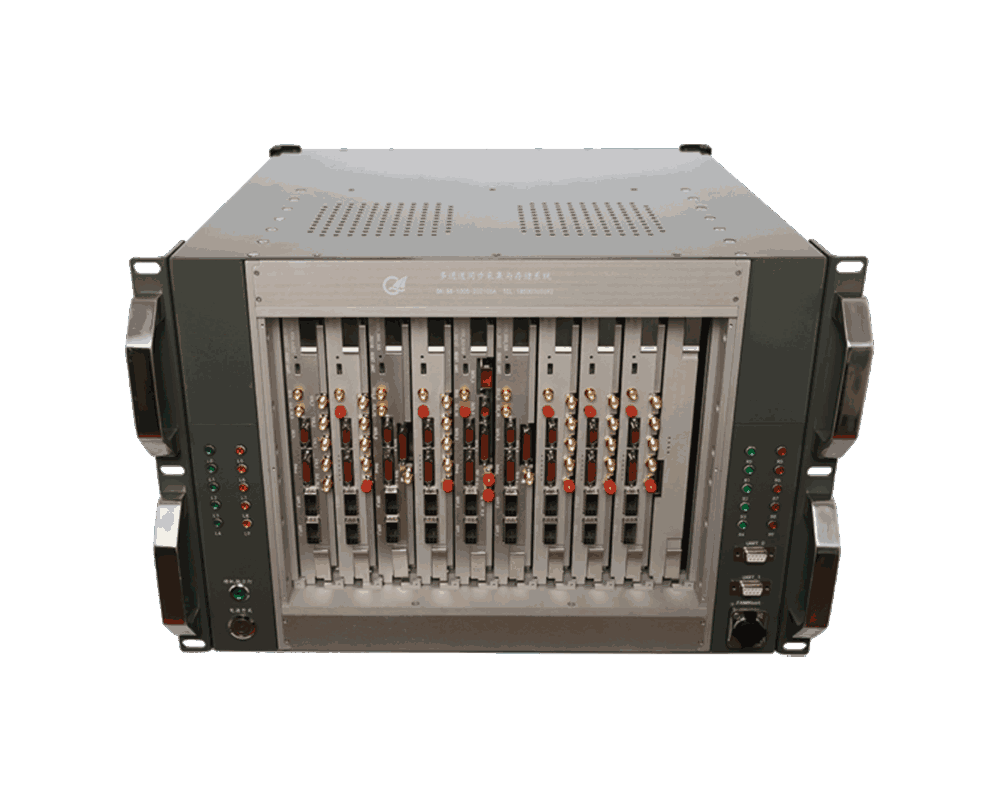

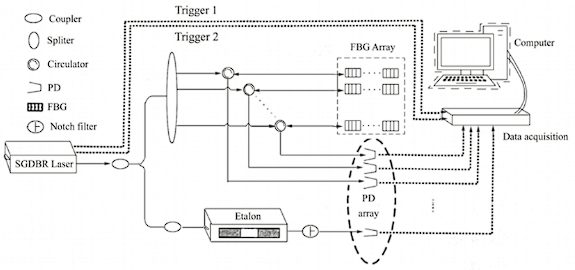

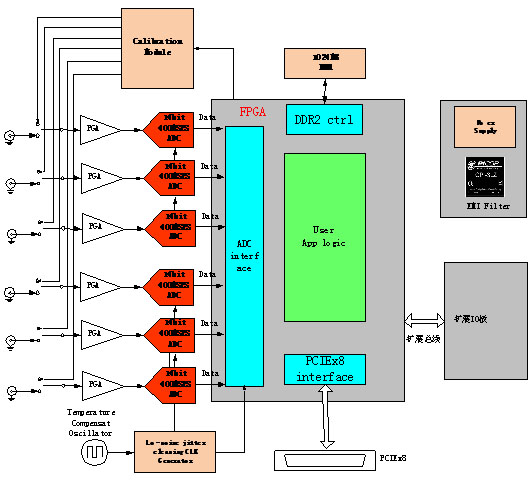

系统采用基于PCIEx8的采集系统,包括如下几个部分:

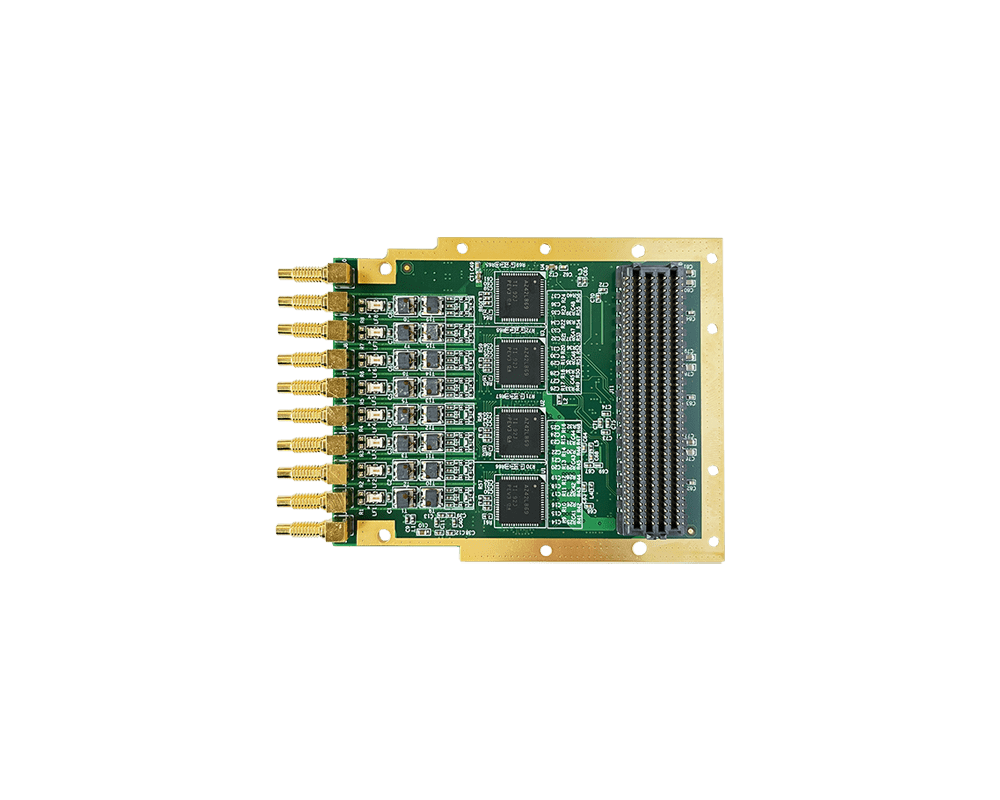

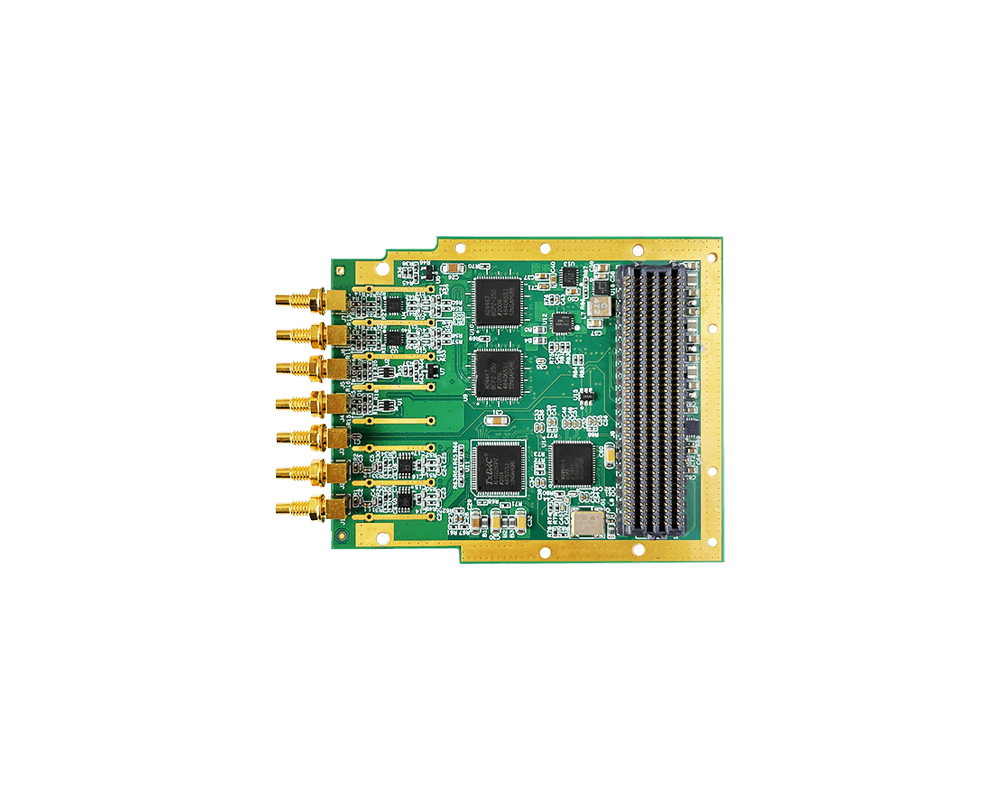

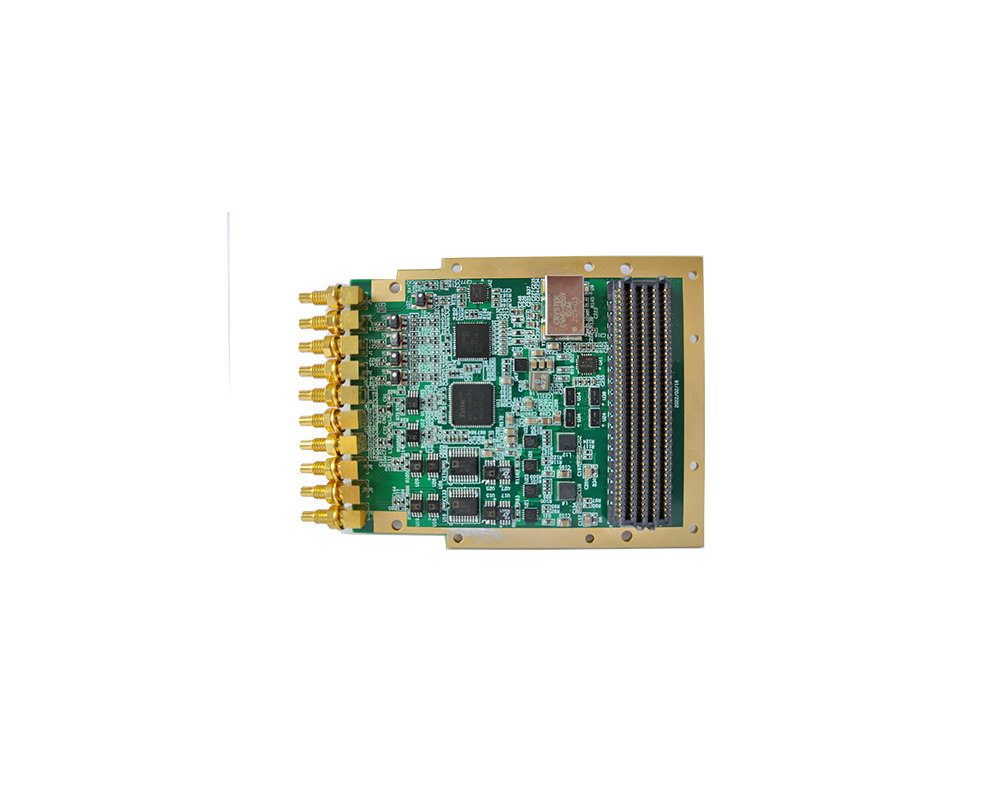

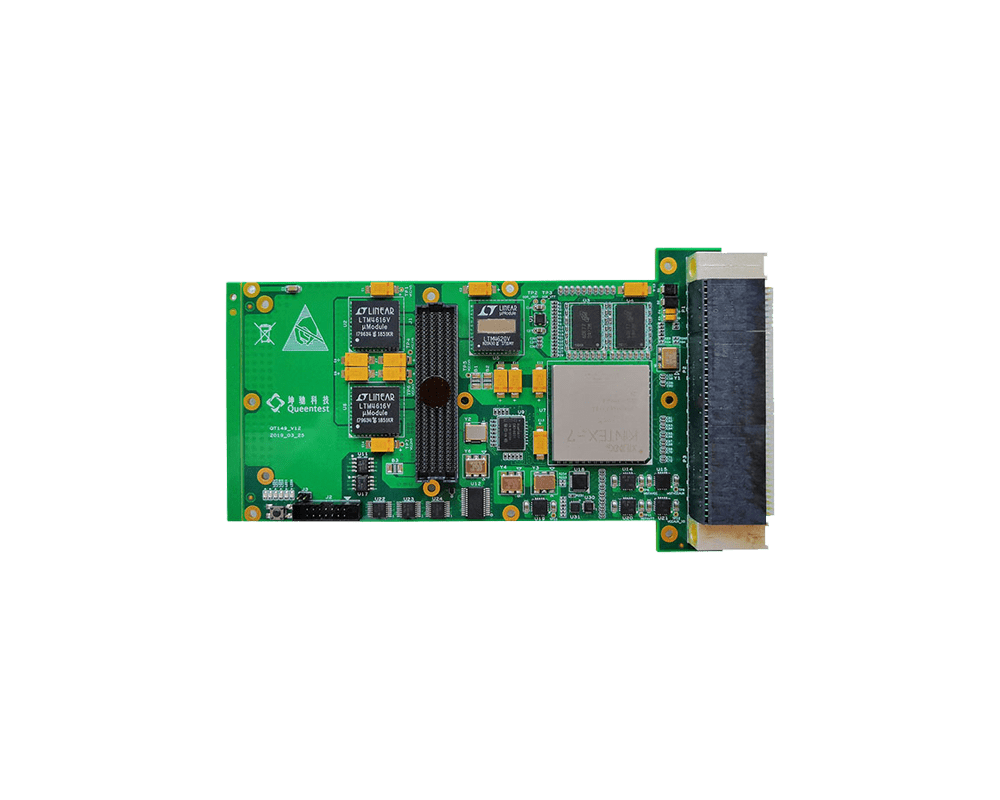

1.14bit400MSPSADC,一块卡中集成6通道。采样率可以通过软件设置。

2.低噪声模拟前端,支持+/-5V~+/-200mV信号输入,1MΩ/50Ω阻抗可选。

3.板载1024MBDDR内存。

4.优化的PCIexpressx8传输接口,支持1200MB/s的连续传输速率。

5.8个可编程GPIO,可用于系统控制。

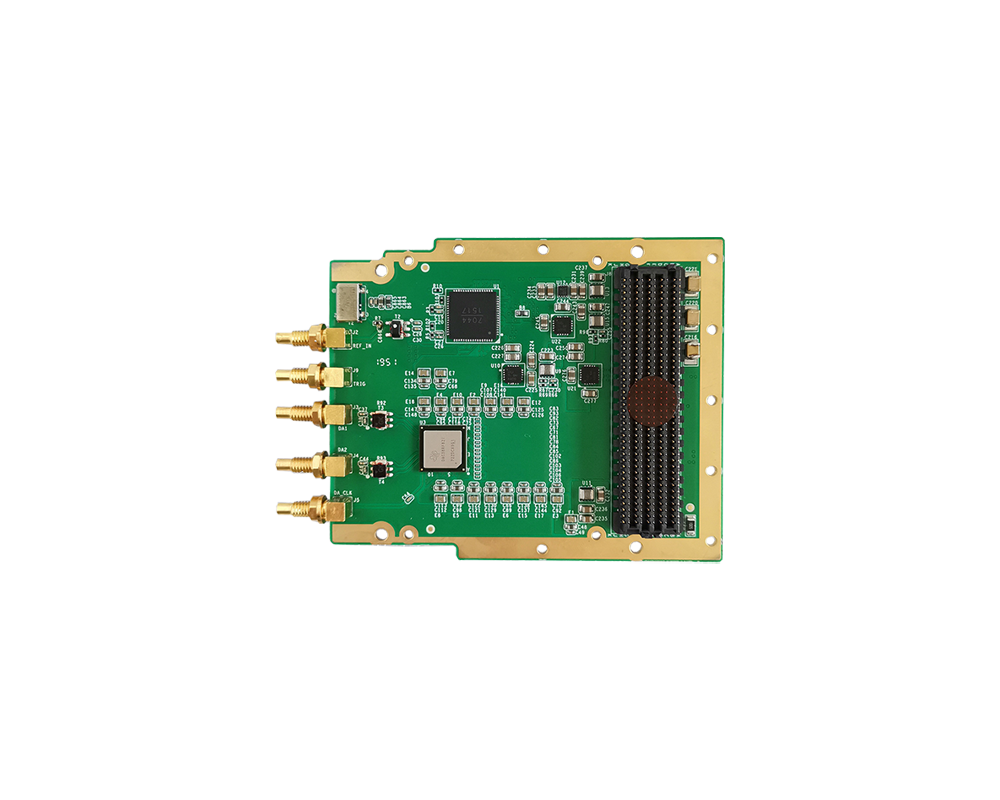

6.高稳定度,超低低抖动时钟发生器。

7.低噪声电源设计。

8.板载高精度校准电路及时钟相位调节电路。

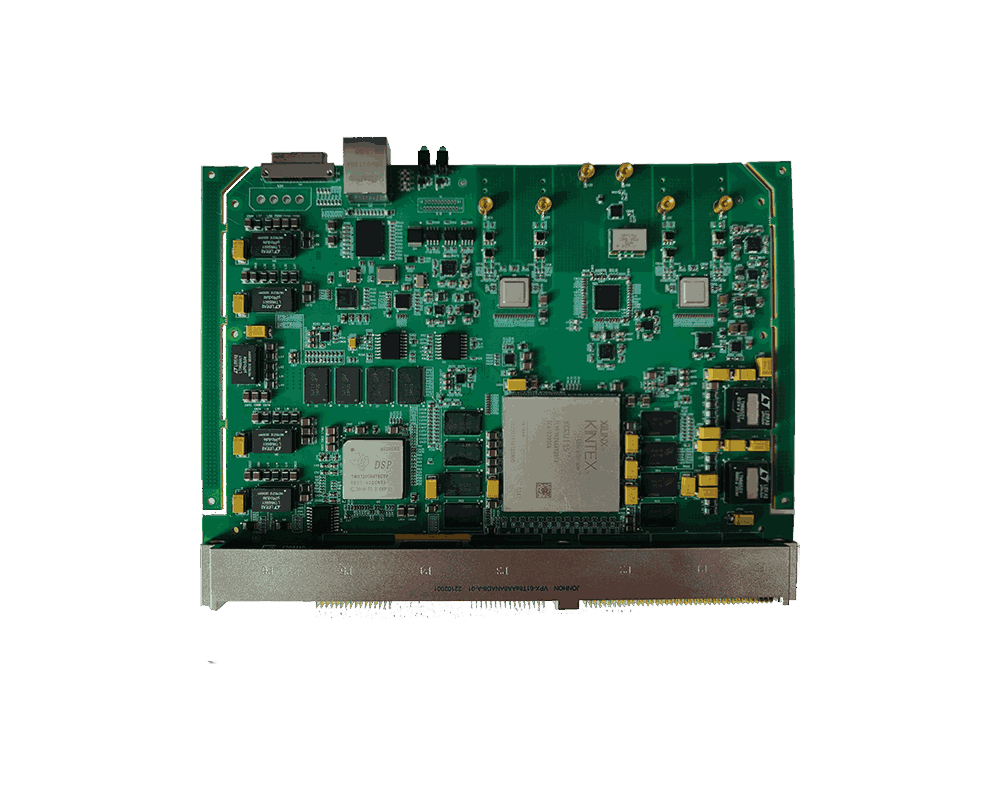

9.板载XilinxXC5VSX95TFPGA,全开放的FPGA逻辑资源,支持用户自定义逻辑开发。

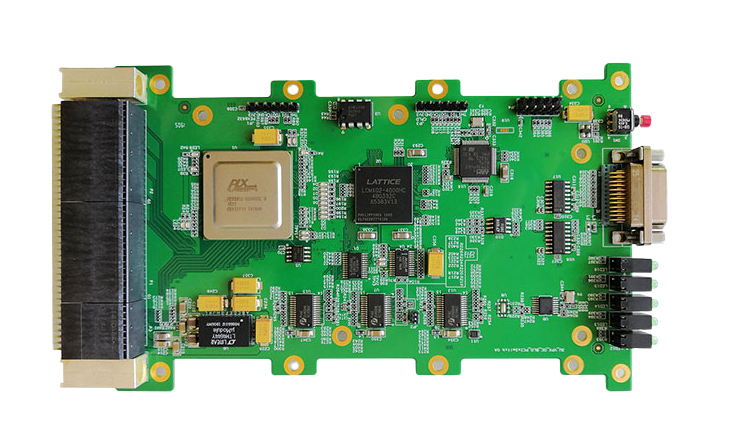

10.提过扩展总线接口,包括LVTTLIO和高速rapidIO接口,方便用户扩展应用;可以设计扩展板直接扣在采集卡母板上。

11.提供完整的FPGA开发工程,包括PCIe,DDRcontroller,ADCinterface等IPcore。

12.提供windows下的驱动程序以及API函数,SDK开发包。

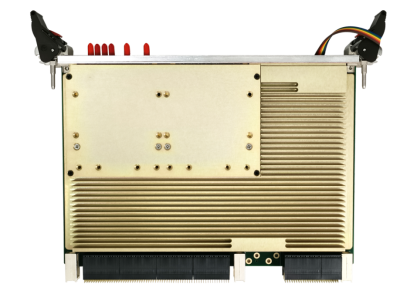

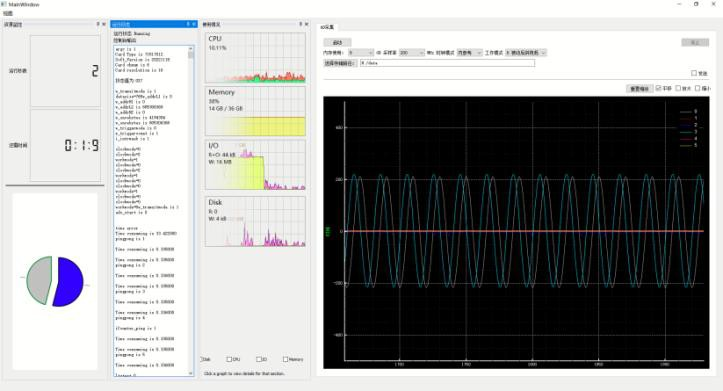

系统整体框图如下:

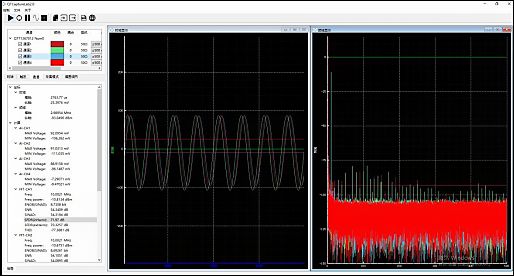

6通道同步采集的精确控制:

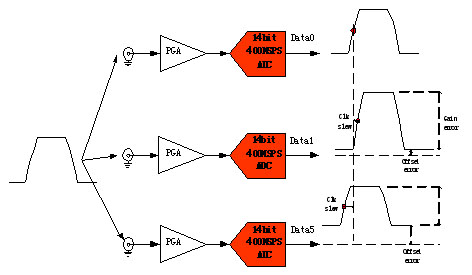

1.首先要保证6通道的时钟严格同步以及每通道的模拟电路以及每个ADC的工作状态一致性。如下图所示:

6个通道的采集误差主要由模拟电路以及不同ADC芯片的clkslew,gainerror以及offseterror组成。尽管我们在设计硬件电路以及PCB设计会尽量考虑以上问题,如同源的时钟分布以及相同的走线;6个ADC公用精准的外部参考电压源等等,但不幸的是,这些设计改进并不能完全消除这些由模拟器件本身的固有特性引起的误差,这些误差是随机的,也随温度变化而变化的。

因此,动态校正电路以及自适应的数字后补偿算法是必不可少的解决方案。

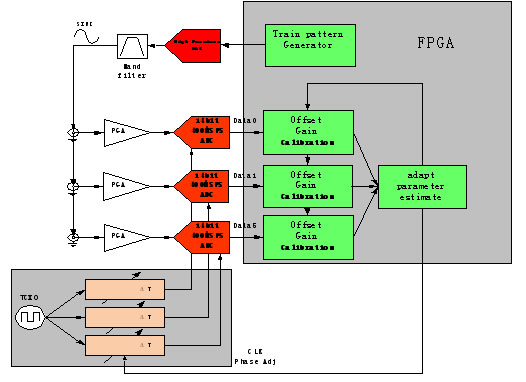

校正功能实现原理如下:

校正功能有校正电路和FPGA算法部分组成,校正电路由高精度低速DAC,参考源,滤波器和时钟相位微调芯片组成。FPGA算法核心为参数估计自适应算法和校正参数逻辑组成。校正目标为设置一个基准通道,其他5个通道的时钟相位以及gain和offset向该基准通道标定。该方法不能校准每通道ADC的绝对精度,而只是每通道的个参数一致,这对测量每通道采集数据的相对相位是足够了!

校准信号为A*sin(ω*t+φ)+B;

CH0采到的信号为A0*sin(ω*t+φ0)+B0;

CH1采到的信号为A1*sin(ω*t+φ1)+B1;

CH2采到的信号为A2*sin(ω*t+φ2)+B2;

CH3采到的信号为A3*sin(ω*t+φ3)+B3;

CH4采到的信号为A4*sin(ω*t+φ4)+B4;

CH5采到的信号为A5*sin(ω*t+φ5)+B5;

通过迭代法解线性方程组,当方程收敛时,分别能得到每个通道的参数,通过计算每个通道的同基准误差,来调节clkphase以及gain和offset来后是6个通道工作一致。

2.为了准确的采集,采集系统的信噪比SNR必须得到保证。影响采集精度的主要要素有以下几点:

量化误差。

Clockjitter和ADCjitter。

数字以及电源干扰

量化精度的提高:

对于量化误差对采集系统的影响,我们在该系统中选用14bit的ADC,理论

![]()

Clockjitter的消除:

该方案中采用温度补偿晶体TCXO以及业内顶级的JittercleaningCLKGenerator芯片来保证clock的稳定性,Clockjitter的消除以及极低的Phasenoise。

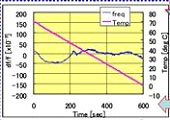

在宽温工作环境下,普通的晶体随着工作温度的变化,晶体的稳定度和频率都会发生改变,为解决该问题,我们在设计中选用epson公司的TCXO,该晶体具有业内领先的温度稳定性,在宽温工作环境下不会超过+/-2ppm,其温度测试性能如下:

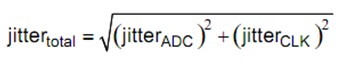

对于时钟芯片的选择,也是基于同样的考虑,集成高精度高稳定的VCO,具有Jittercleaning功能和clkphaseadj功能。通常,jitter由ADC本身的jitter和CLKjitter组成,各自的RMS再组成总jitter的RMS:

总jitter的RMS会在采集系统中产生白噪声,其关系如下:

采集系统的总和

![]()

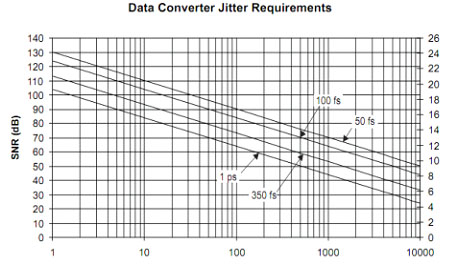

采用本时钟解决方案,其总的clockjitter在系统中完全能做到<1ps。在忽略信号noise,DNL等情况下,fin和clockjitter有如下关系:

系统电源干扰的解决方案:

1.电源抑制(PSR)是采集系统的比较重要的指标,高的PSR能拟制电源上的CML共模噪声,该方案中选用的ADC具有80dB以上的电源拟制比。

2.有效的数字-模拟电源隔离和滤波电路。本方案中采用PICOR的专业有源EMI滤波器,能在电源上产生65dB的共模制比和80dB的差模拟制比,远远高于通用的磁珠等EMI滤波效果。

3.合理的PCB布线和接地

价格:不含增值税终价13.6万/张