量子加密通信验证系统

量子加密通信验证系统

1.概述:

项目背景:

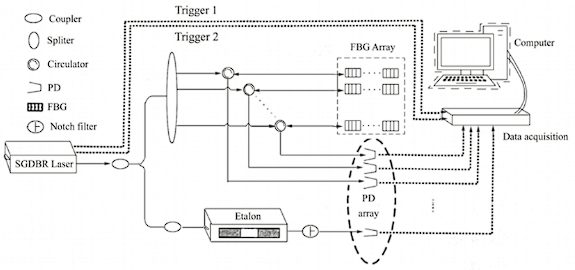

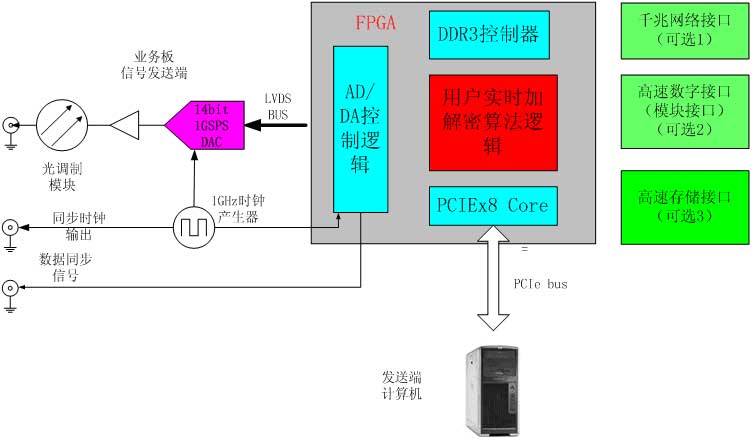

本系统通过基于PCIE总线的高速ADC采集和高速DAC回放系统,实现量子加密通信中的实时大数据量传输、同步接收和量子加解密计算。系统中高速信号发生与同步采集系统主要用于高速光调制信号的产生和在接受端进行同步采集功能。通过系统通过PCIEx8总线与计算机进行通讯(或者通过单独的数字IO),同时能将需要输送到光调制模块的数据实时的从计算机中传输到光调制模块上;同时在接收端同步采集光模块的解调信号并将解调的数字信号传输进计算机中。板载的FPGA可以进行实时的高数据带宽的量子加解密运算,大大减轻计算机的负担。

我们面临的挑战:

1、量子加密通信采用光通信模式,需要设计复杂的光电转换设备。

2、收、发数据两端距离较远,需要解决远距离同步问题。

3、加密算法数据量大,且要求实时性;FPGA并行算法开发复杂度较大。

4、由于接收和发送均采用光脉冲信号,这就需要特殊设计ADC的前端放大器,和DAC的输出驱动器。

5、高速ADC和DAC芯片时钟速度快,数据线多,对FPGA接口的时序要求非常严格。

解决方案:

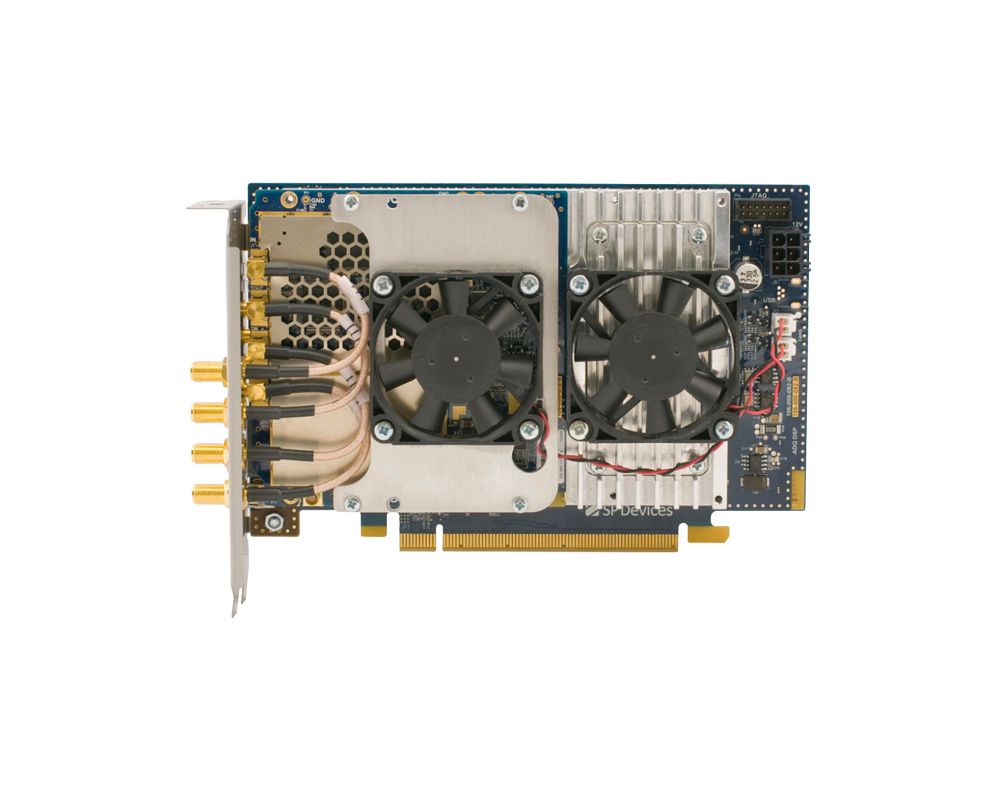

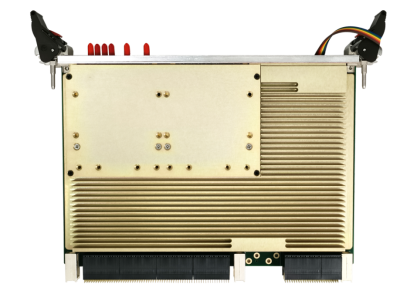

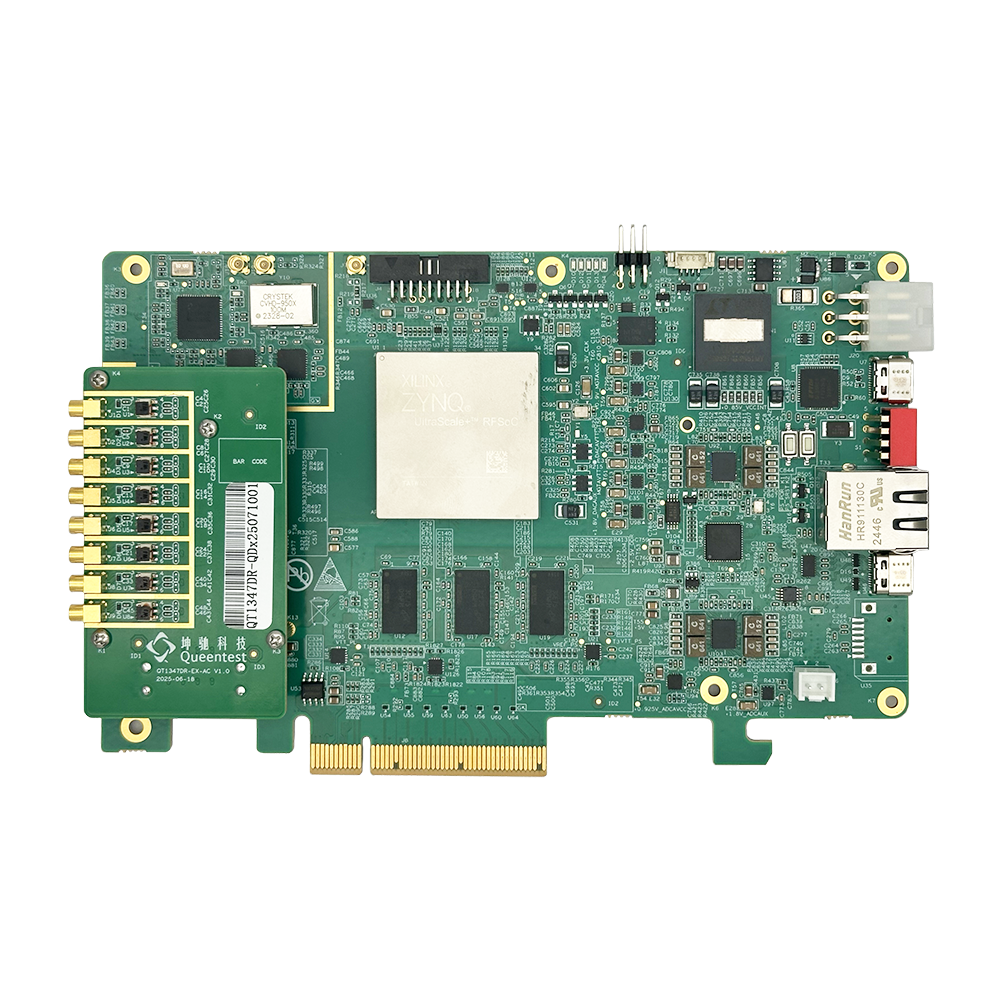

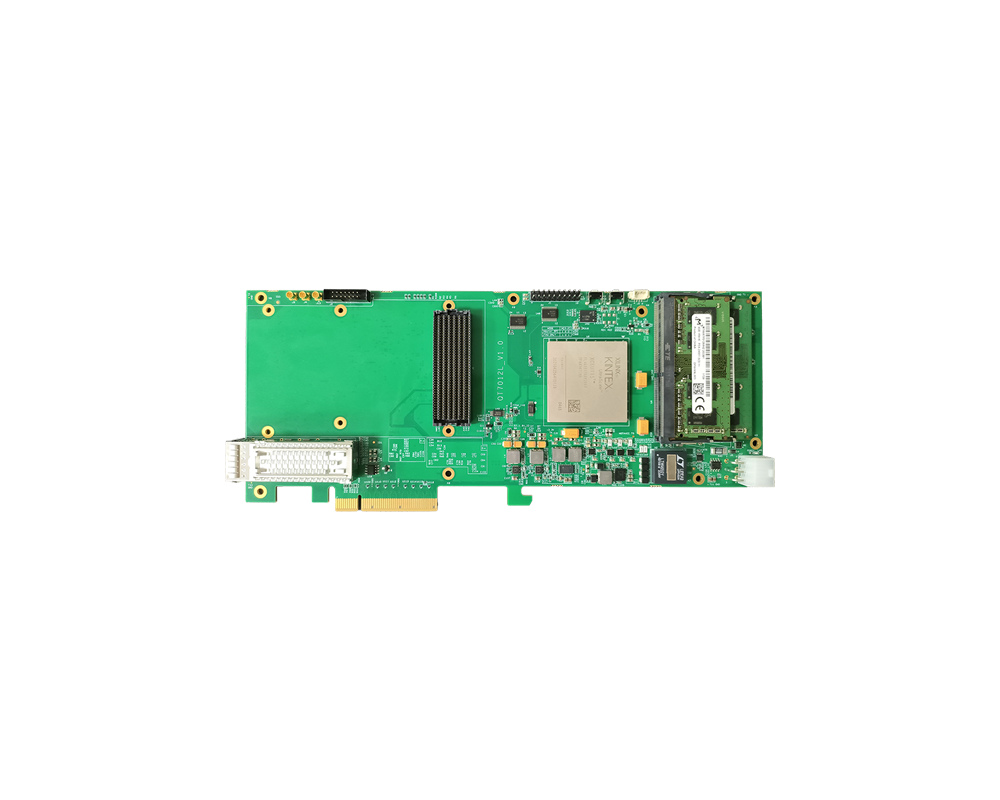

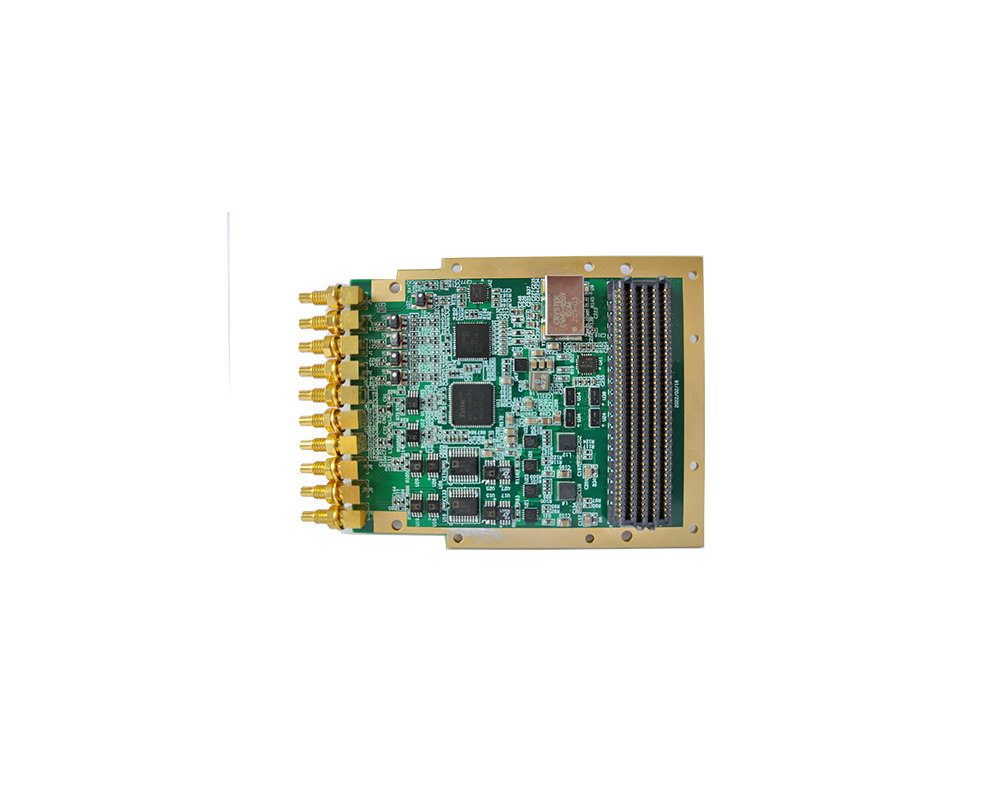

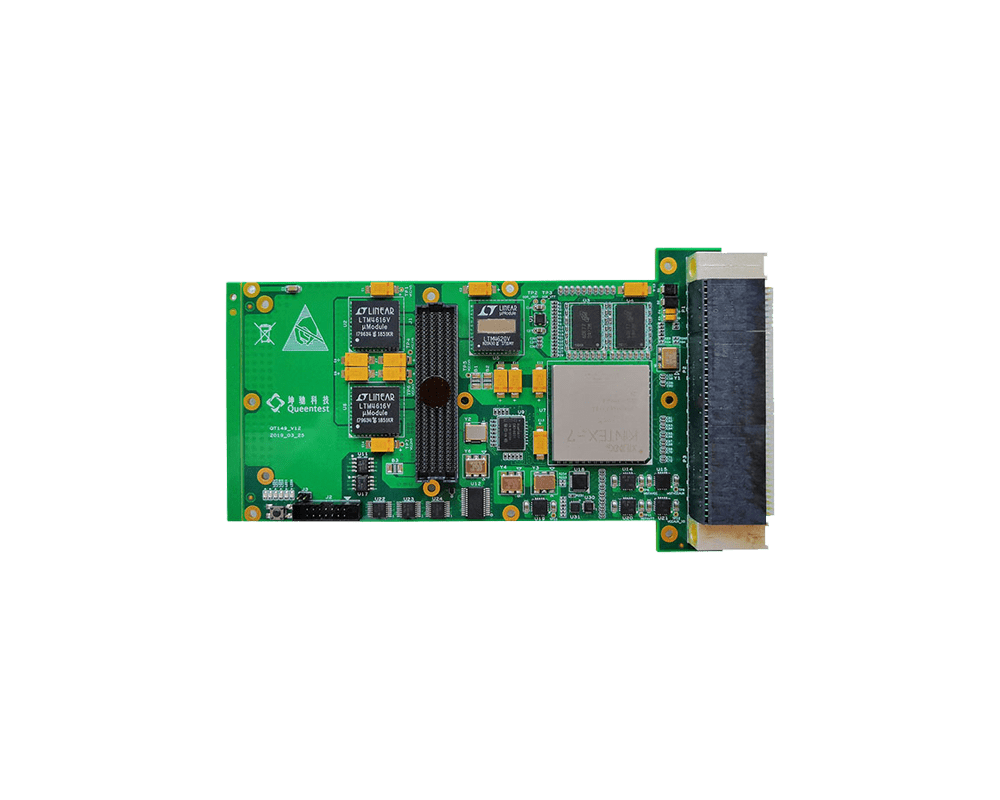

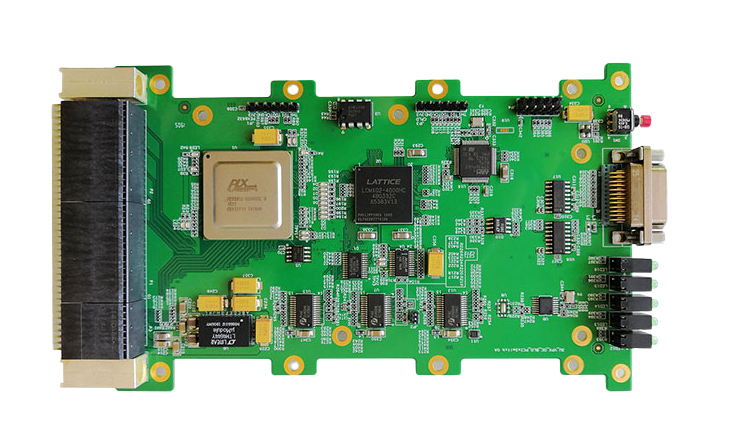

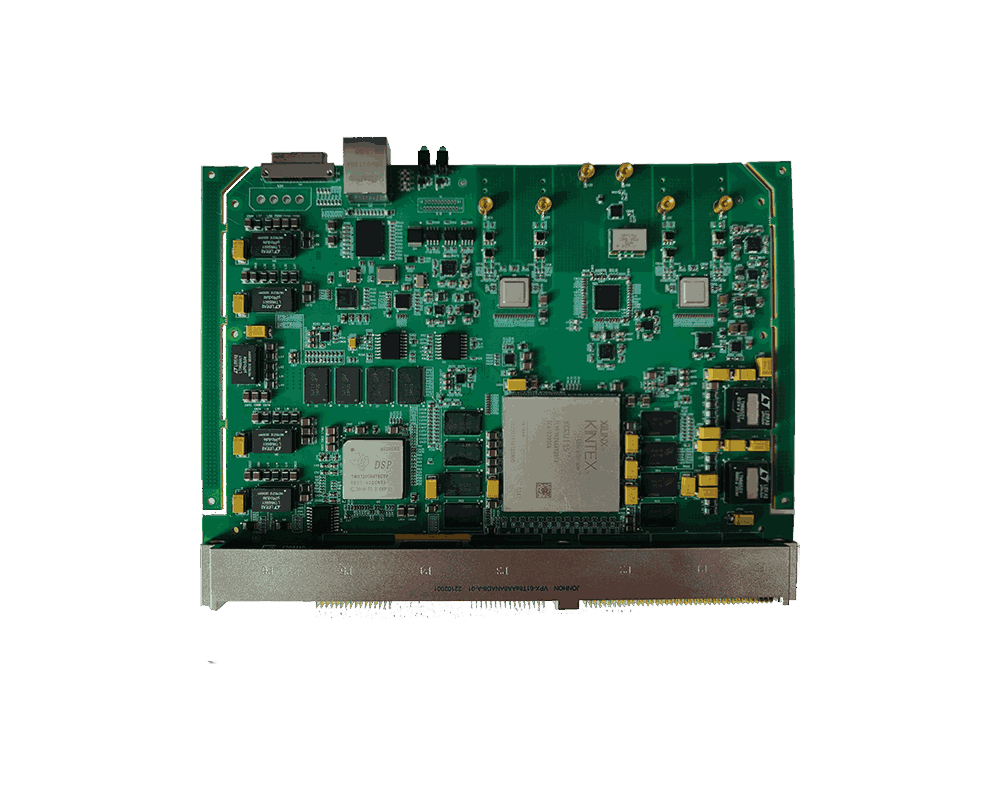

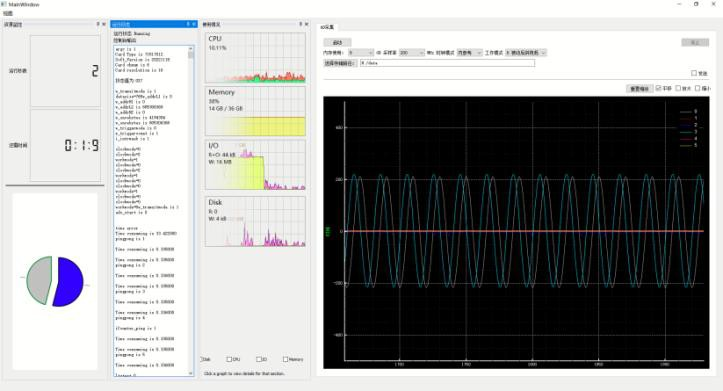

整个系统由自行开发的高速AD/DA模块(集成PCIE接口和DDR3高速储存单元)和工控机业务板分为发送端部分和接受端两部分,板载一块Xilinx公司V6系列FPGA进行统一的系统逻辑控制和数据转送转换。

发送端:

位于工控机中的PCIE接口主要负责将发送端用户数据的发送到业务板的高速DAC上,采用采用8xPCIE高速接口,大可以产生1.5GB的连续读写数据流

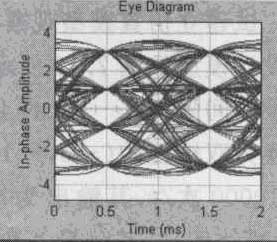

终在DAC输出产生符号率为1024的模拟信号:

14bit高速DAC,支持500MSPS的数据率,1GHz的采样时钟驱动。14bit位宽,保障1024符号率的数据足够的信噪比和无INL误差。

1、高板载4GB内存,PCIEx8接口,支持1.5GB的连续数据传输速率

2、能实时并重复放送4G采样点用户数据。

3、高速1GHzDAC时钟产生和驱动,数据同步的时钟与同步触发信号输出。

4、板载高速大规模FPGA,用户可自定义逻辑。

5、高速信号放大输出。

6、可编程低抖动时钟发生器。

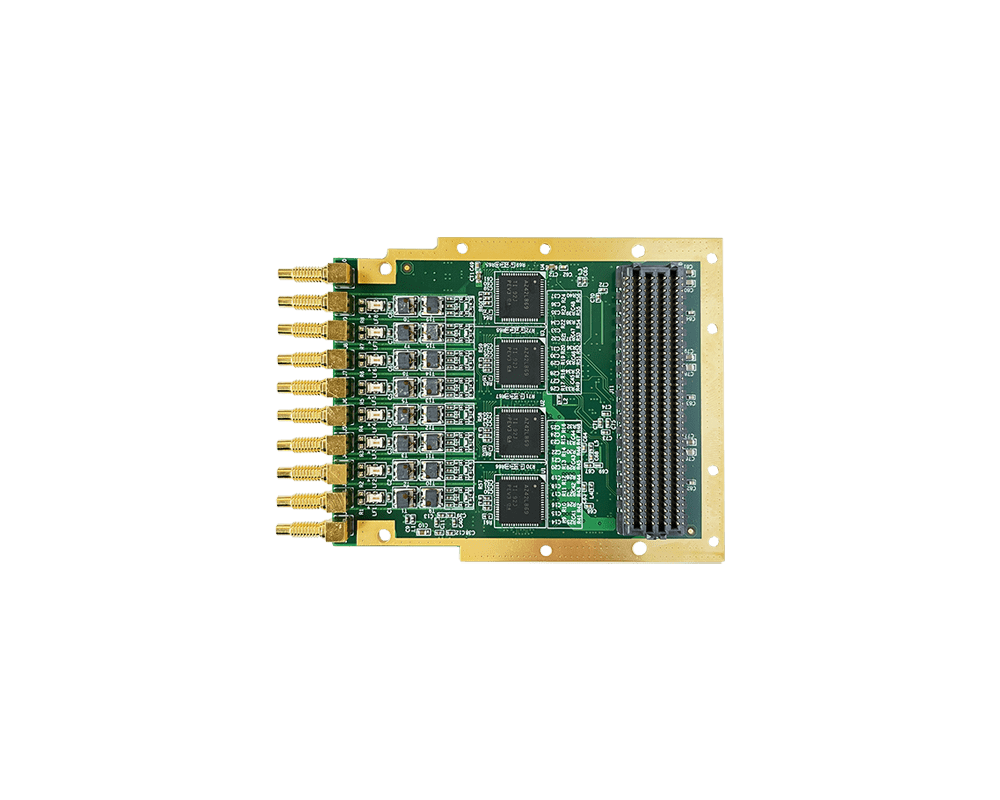

接收端

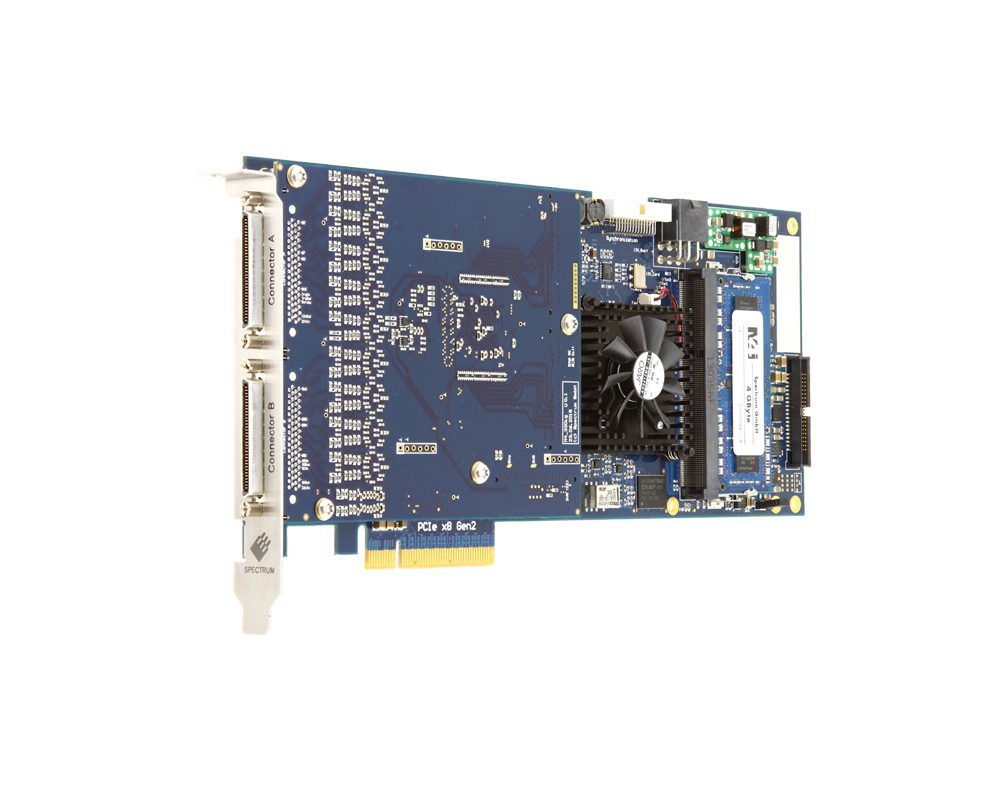

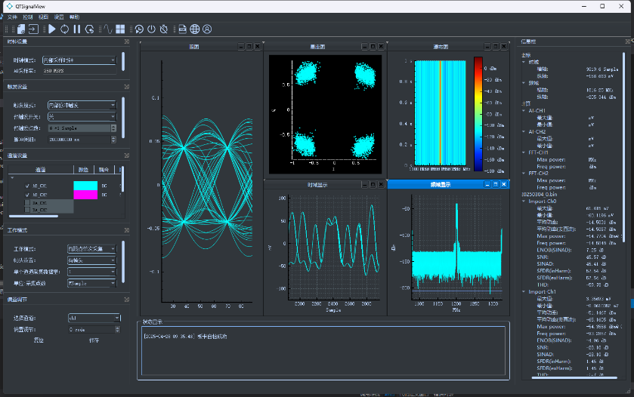

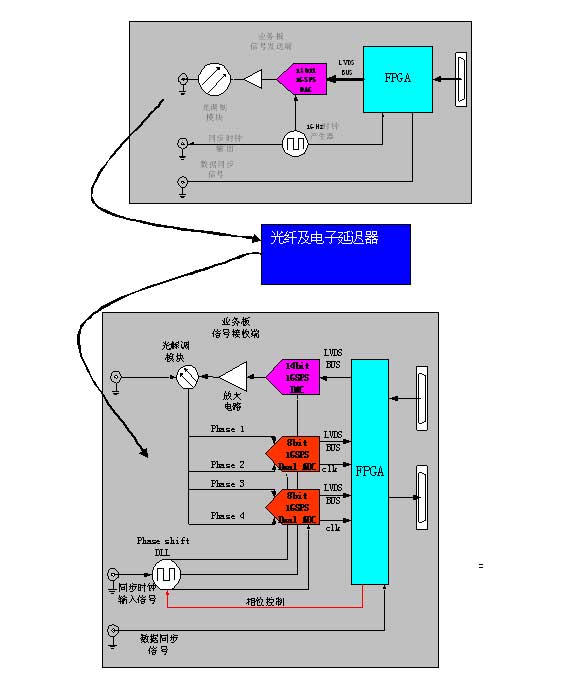

同理,接受端也部署了相同的发端系统用于解调。同样需要业务板上的高速DAC和PCIE高速接口传输数据。为采集光解调模块输出的4个相位的3电平信号,我们在接收端业务版上安置了2块双通道高速ADC,采样率为1GSPS,8bit精度。由于采样数据只是3电平归零码(RZ),经过转换后变为1bit归零码(NRZ),因此我们采用PCIE接口同步接受ADC的输出数据就可以满足带宽和容量的需求了。

系统各功能模块描述:

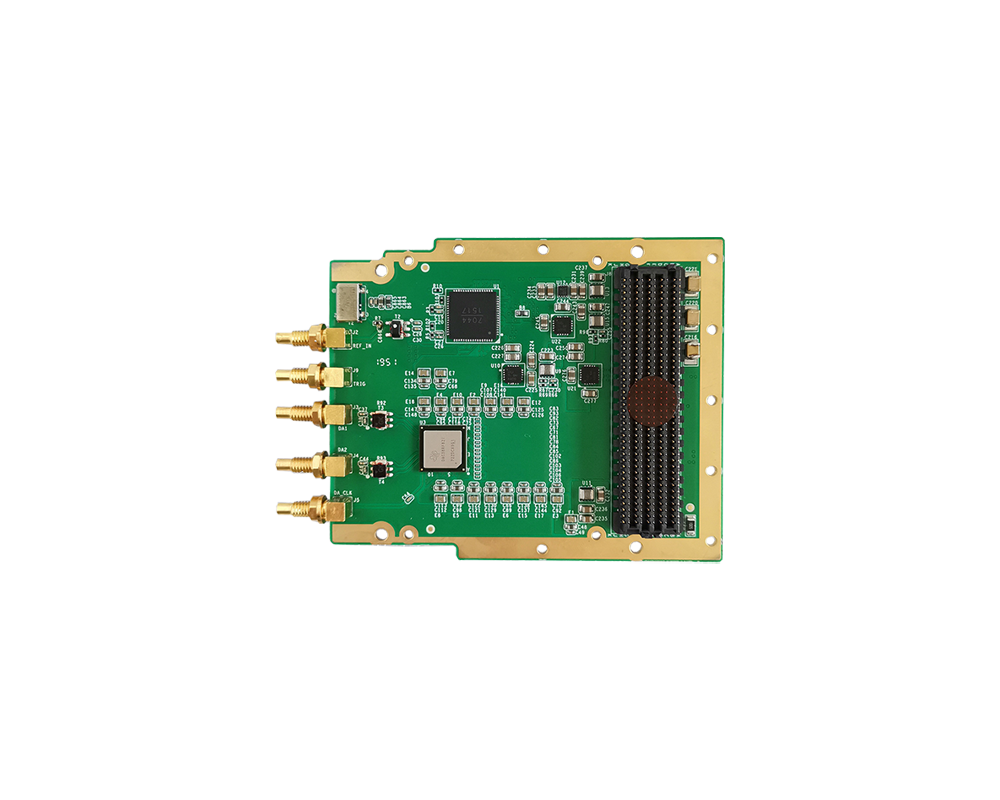

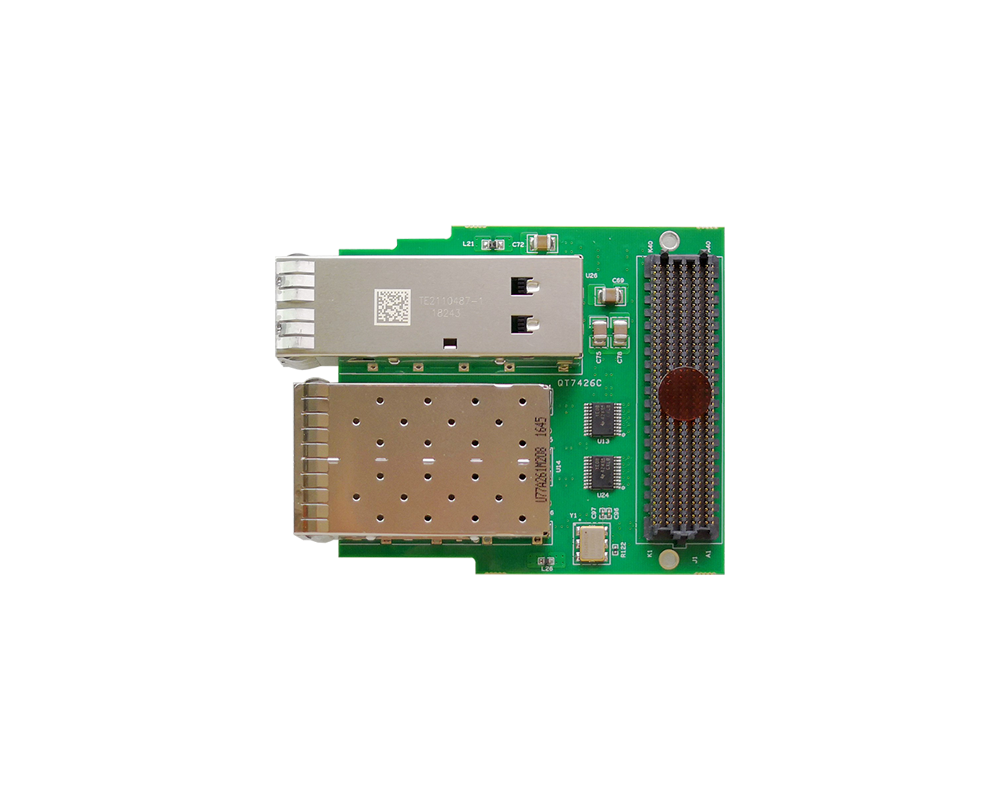

高速DAC接口

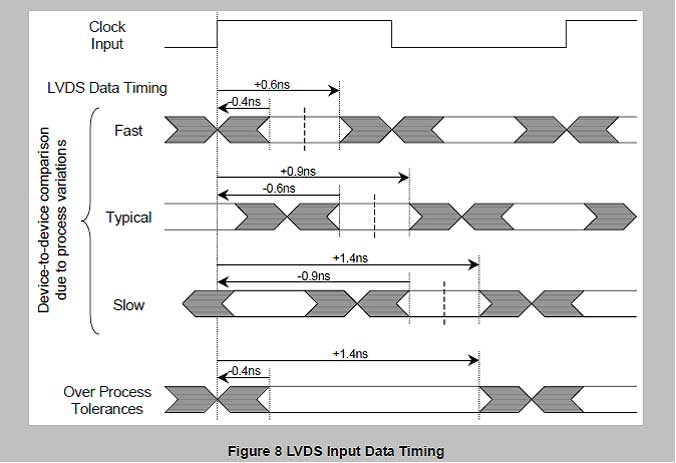

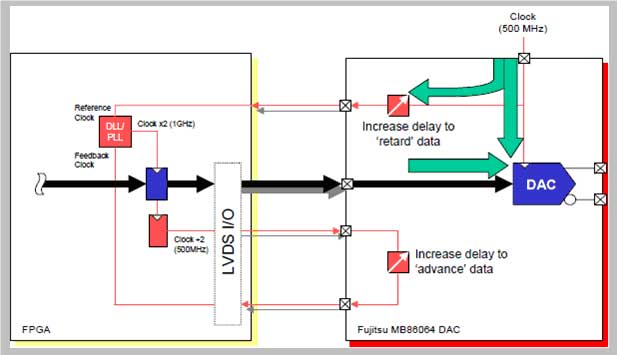

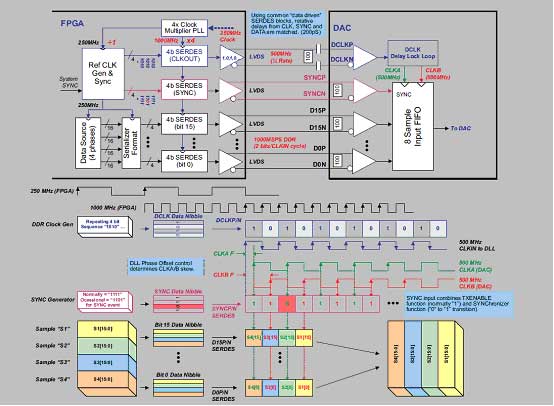

由于绝大多数FPGA芯片都无法工作在1GHz时钟频率下,我们选用的DAC芯片提供了双通道LVDS接口,将数据率减小到500MSPS,减小了FPGA设计难度和提高了系统的可靠性。

DAC同FPGA的接口为LVDS

上图所示,数据DDR形式,数据的速率为时钟的两倍。

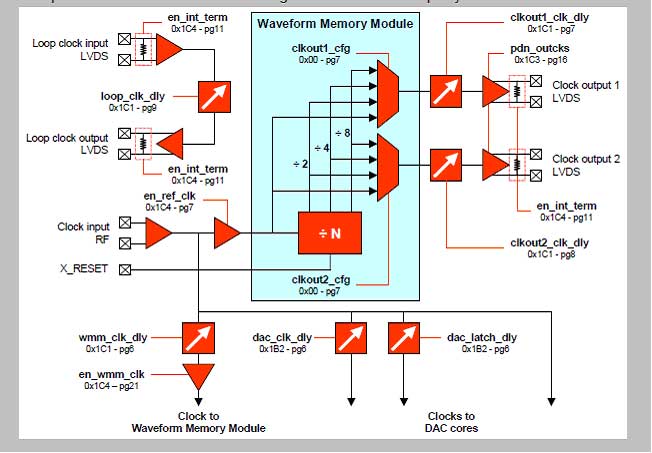

时钟方案如下所示:

DAC的时钟有着特殊的设计,可以通过环回来抵消PCB的延迟,从而更能可靠的传输数据。

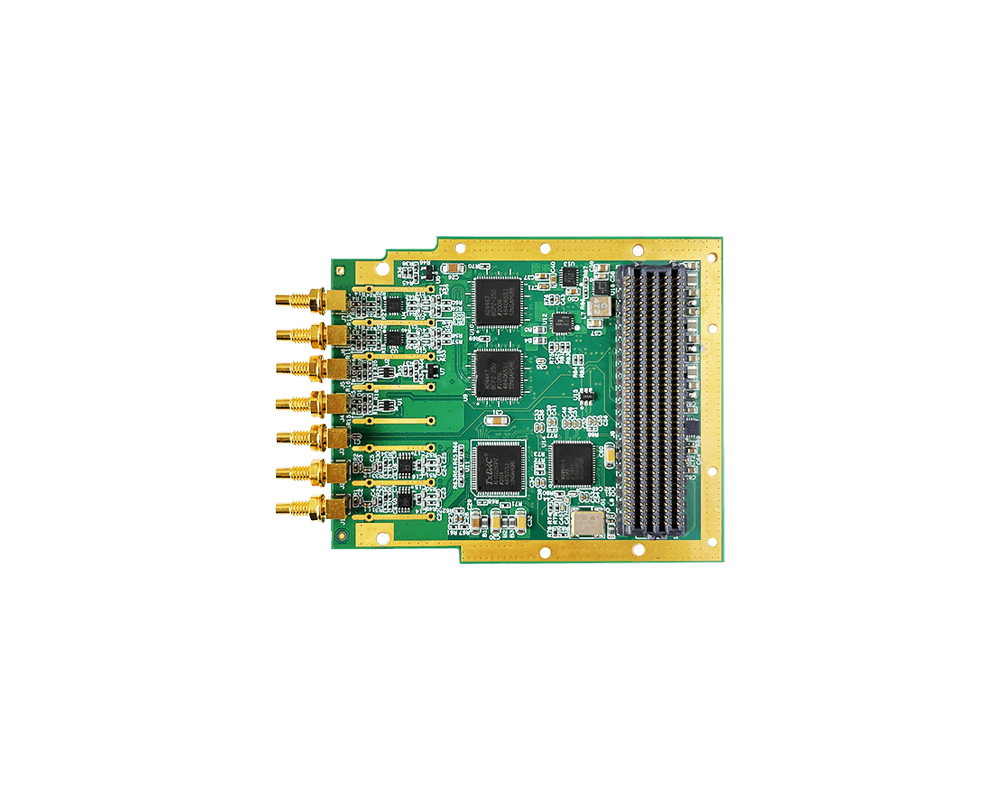

1GHzSPSADC方案:

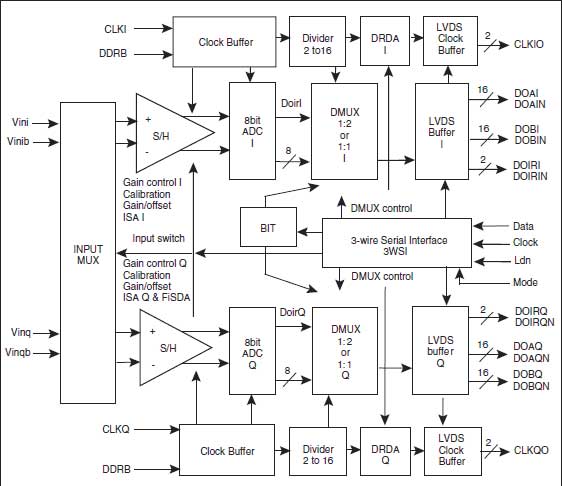

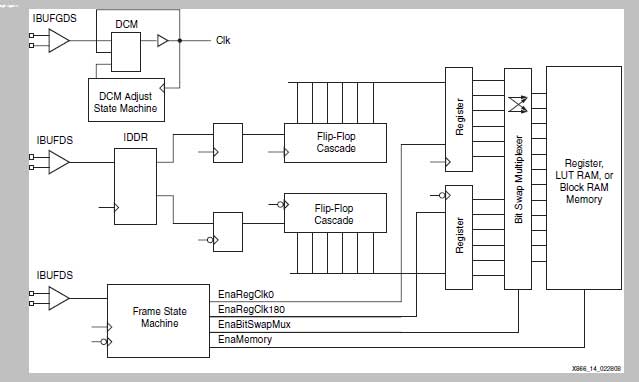

我们采用两片Dual1GSPS8bitADC作为光解调信号的采集器。

其框图为:

系统中我们采用两片DualADC组成4相位的时间交错采集系统,来分别采集光解调器输出的4个不同相位的1GSPS归零码数据。

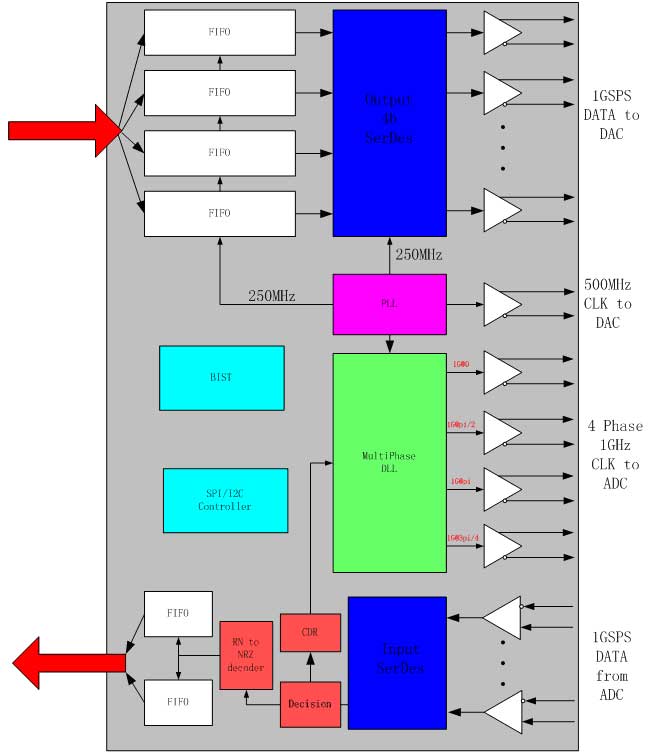

4.4FPGA逻辑方案:

FPGA整体方案如下所示:

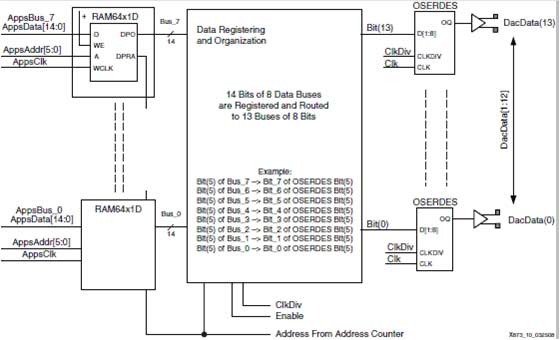

4.4.1发送端FPGA逻辑:

由于IP限制,该模块并不能支持3b(3倍频串行)传输,只能4b,8b等倍率传输,这就限制了我们大利用数字板卡带宽的想法。只能采用如下方式进行数据编组:每块卡32bit编为两组,高10位和低10位;工作在125M下,输入到FPGA后合并为250M速率的10bit数据。系统共用4块卡同时发送250M速率的10bit数据,我们就得到4个相位的数据,在FPGA中进行串行化,终得到1G速率的10bit数据。

发送端的FPGA逻辑如下图所示(14bitDAC):

输入端需要加入同步FIFO进行各通道数据的对齐。

4.4.2接受端FPGA逻辑:

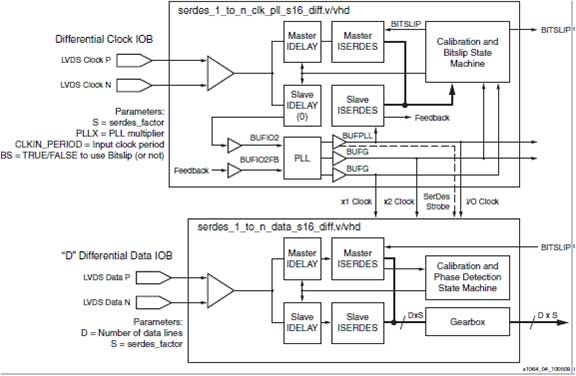

接收端要输入1GSPS@8bit的数据,同样要使用到ISERDES模块,包括时钟驱动部分的逻辑如下图所示:

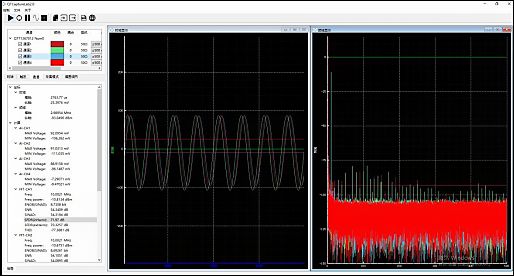

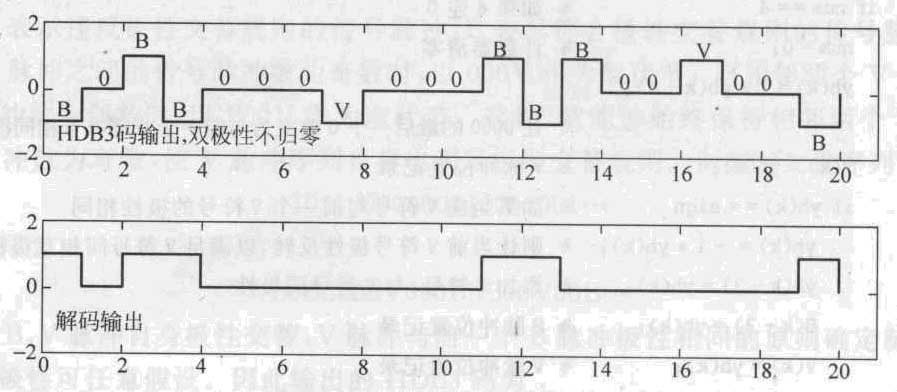

当数据完成交错采集后,进入判决器模块,判决器将8bit的模拟信号判决为归零码,再经过归零码到非归零码解码器进行解码:

输出为1bitNRZ,终输出到PC中的数字IO卡中。这样大大降低了数据速率,同时数字板卡一次也能存储更多的捕获数据。

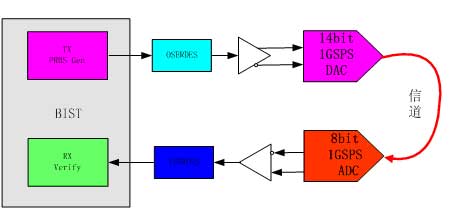

BIST(Buildinsystemtest)模块方案:

BIST模块通过产生或接受PRBSpattern和特定pattern,来自动测试整个数据传送链路各个节点的工作情况,并能计算BER(误码率)。

模式1:

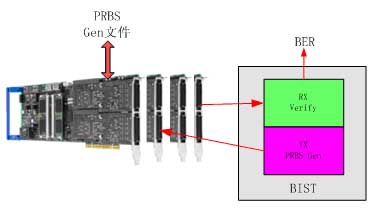

校验数字IO卡输入/输出同FPGA间的链接通道。

PRBS文件从PC经过IO卡送入FPGABIST的RX模块,进行实时校验。

FPGABIST的TX模块发送PRBSPattern,经过IO卡送入计算机,在进行PC上校验文件。

BIST模式1

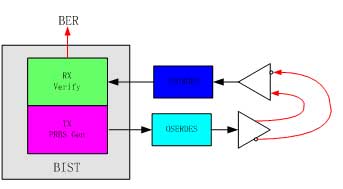

模式2:

ADC和DAC通道间的环回校验。主要检测serdesTX端和RX端分别同DAC和ADC间的链接正确性。

BIST模式2

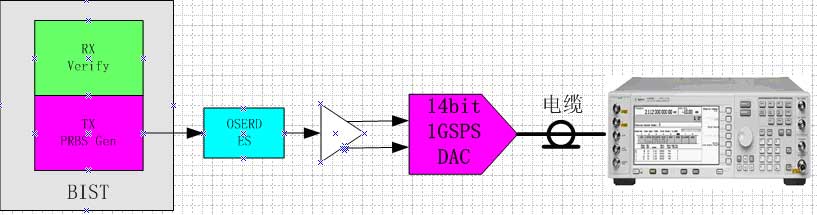

模式3:

发送端的校验,通过BIST模块发送PRBS,经过serdes以及DAC,输出NRZ或RZ码,接BERTEST仪器分析发送端的数据正确性。

BIST模式3

模式4:

整个链路的自环回校验,可长时间计算BER。

BIST模式4

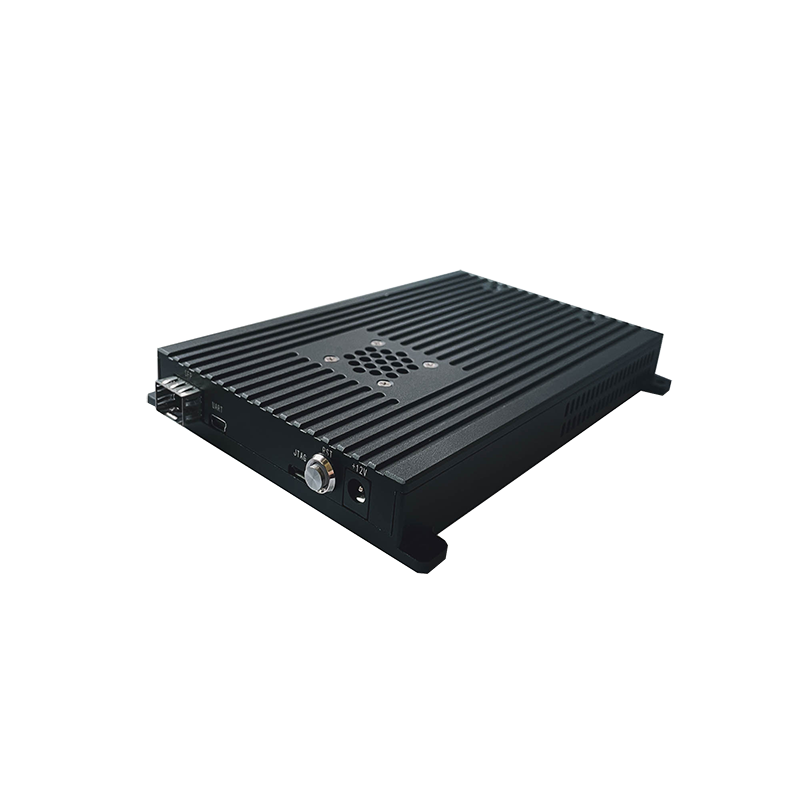

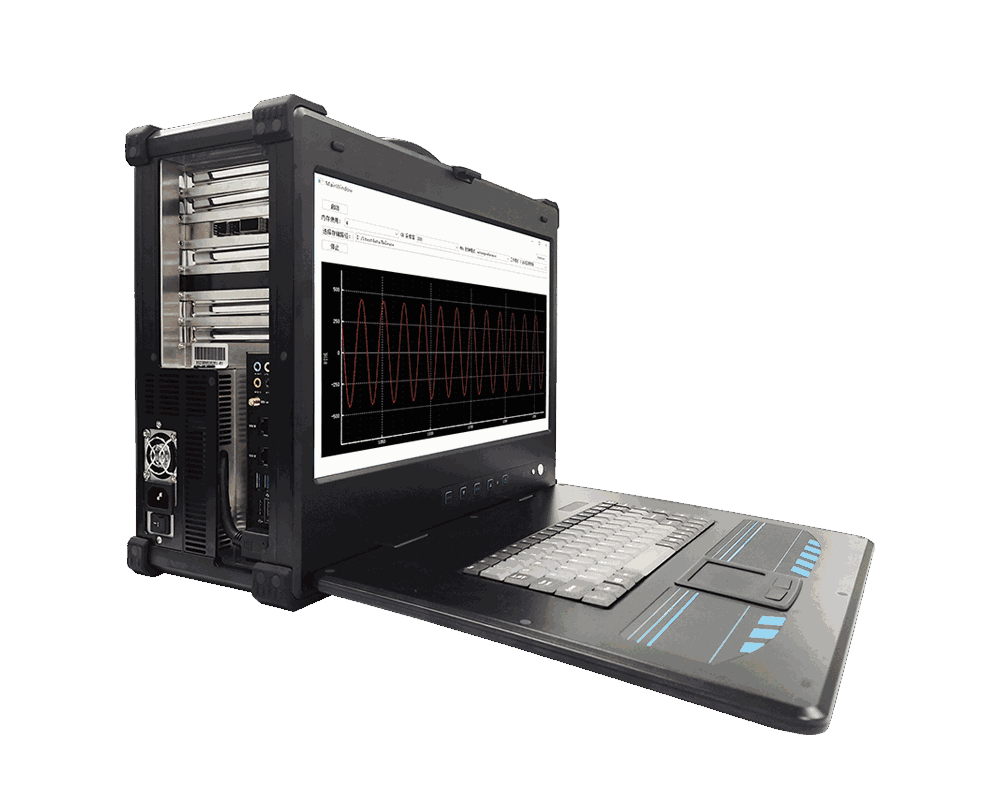

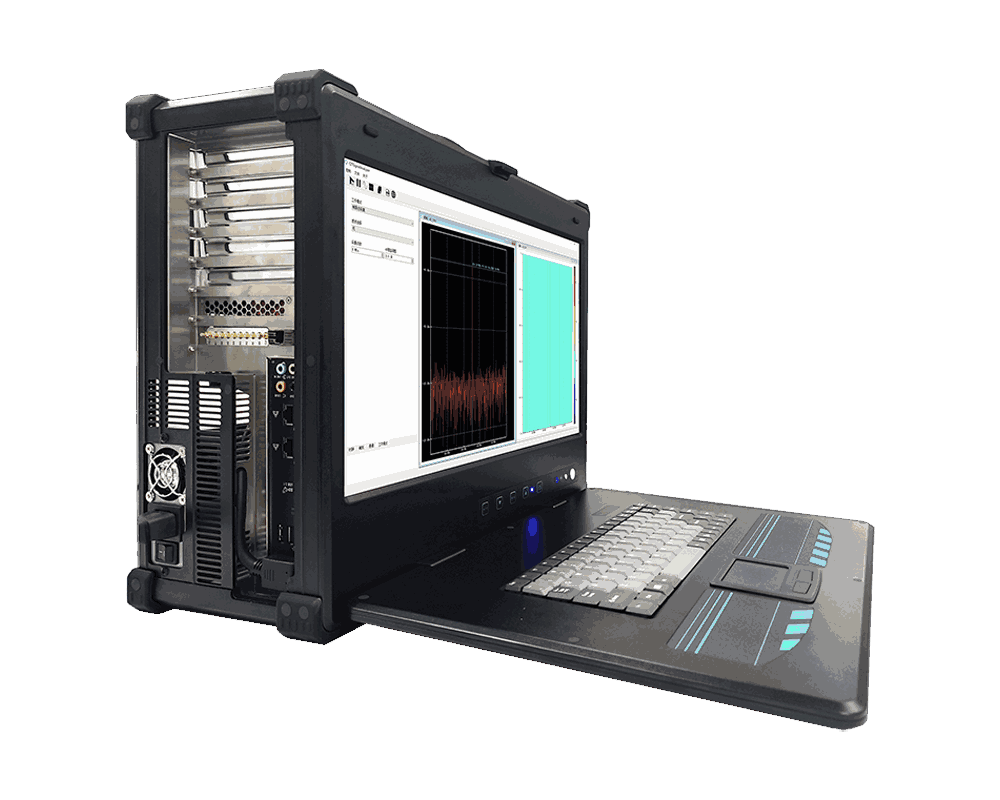

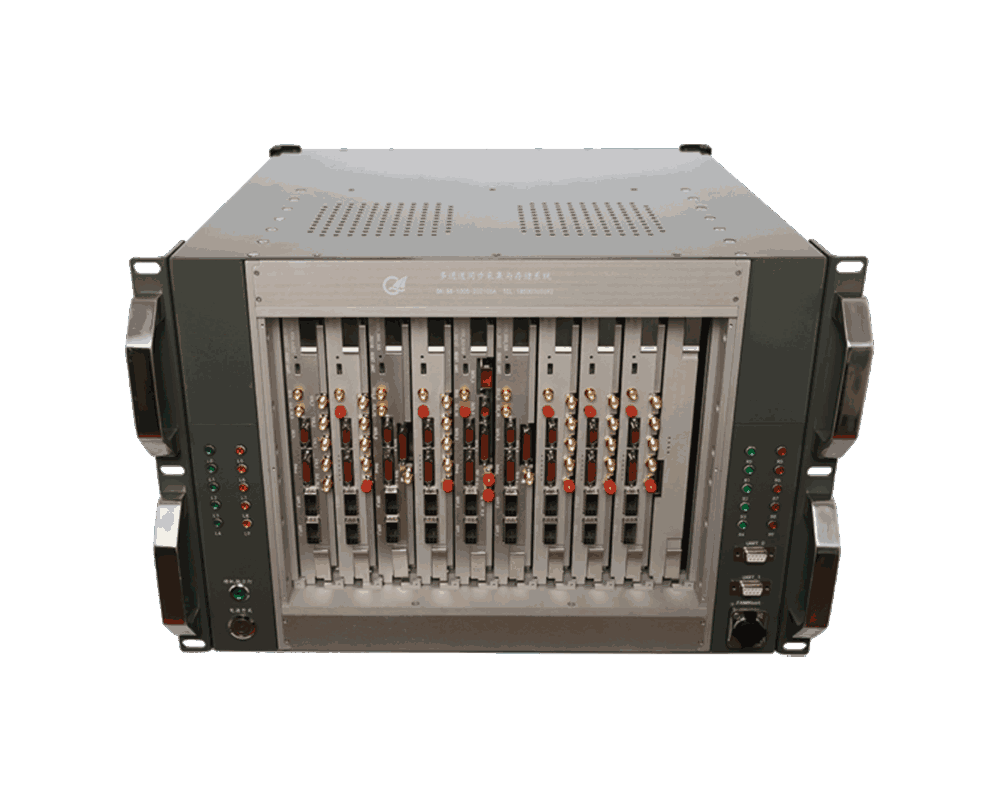

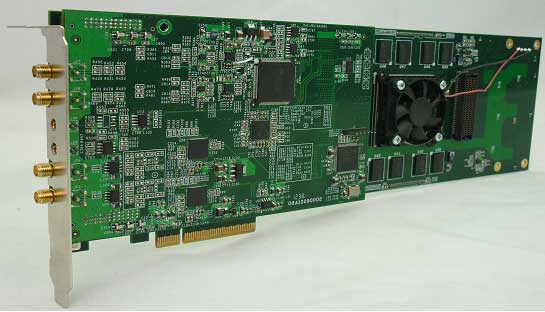

系统实物图和应用环境:

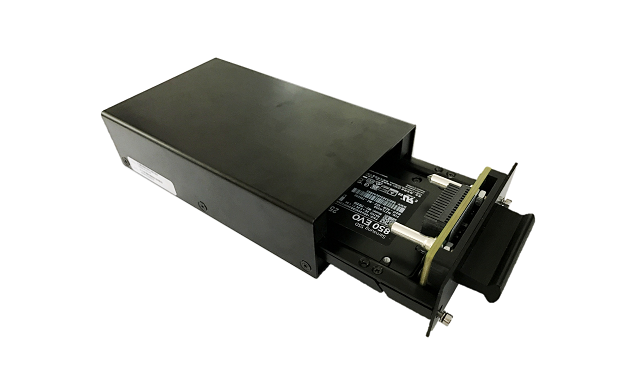

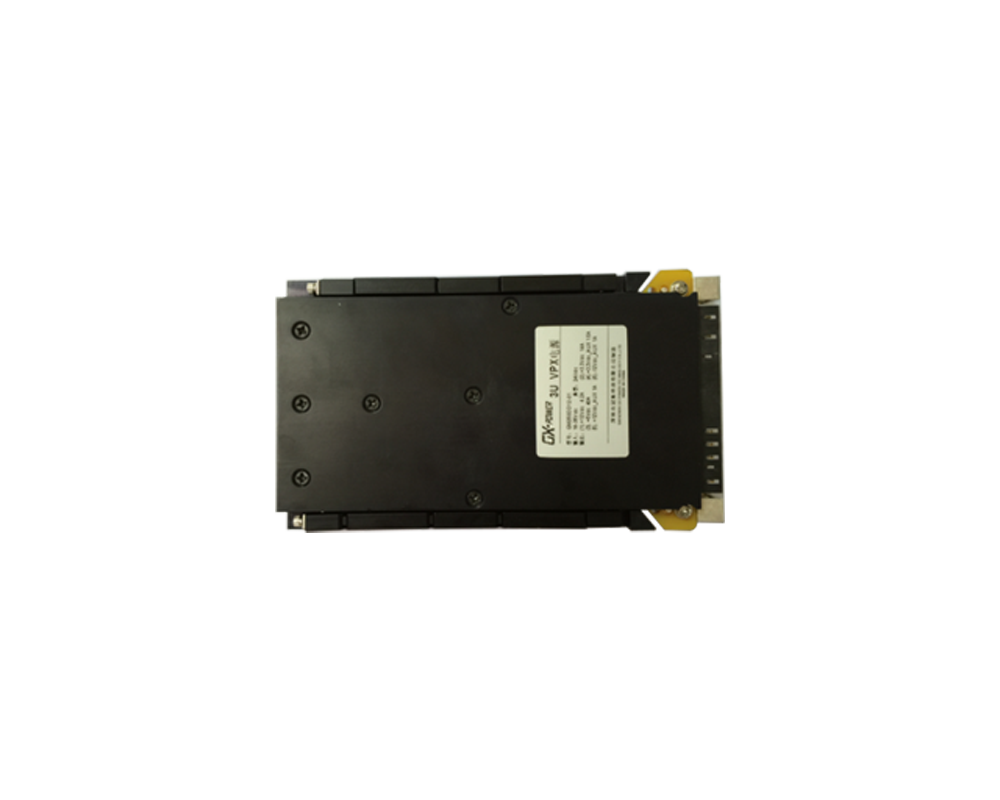

同步收发模块实物图:

收发模块同步工作实验:

系统光路传输环境: