热搜关键词: PCIe高速数据采集卡RFSOC高速数据采集软件无线电平台VPX高速数据采集卡高速信号采集卡PCIe数据采集数字信号处理

✕

ADQ的固件选项FWATD(高级时域)是为极端动态范围而设计的,在高动态范围内,很少出现的弱信号可以和强信号(指高幅度的情况下)共存。我们提供了几个步骤的噪声抑制,并可以结合起来达到所需的性能。固件选件FWATD包括高级时域测量并受益于极高动态范围,典型应用包括:

科学仪器

飞行时间

质谱

电子顺磁共振

粒子物理实验

测试与测量

分布式光纤传感

为了获得极高的动态范围,需要考虑几个参数。固件包含四个级别的噪声抑制, 基线稳定,线性滤波,非线性阈值和波形平均,并且提供了三种专门针对系统噪声(模式噪声)的方法。FWATD可以看作是具有上述噪声抑制方法的工具箱。由此,应用程序可以选择合适的工具以获得所需的动态范围。

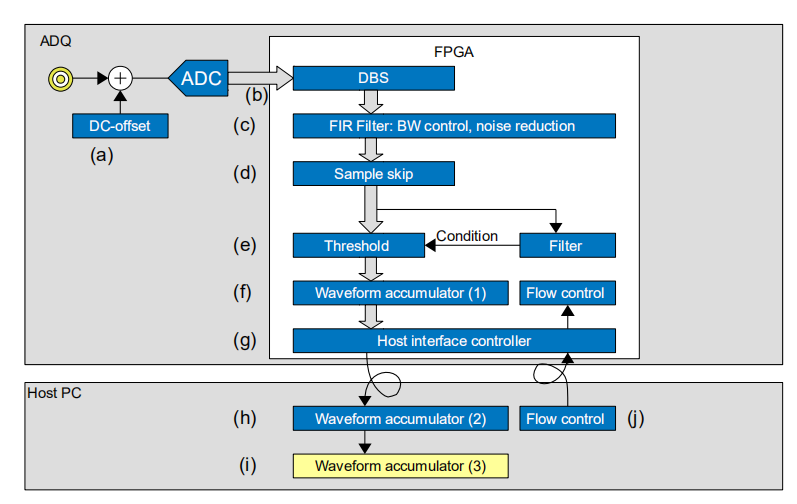

在多通道ADQ中,每个通道有一个FWATD单元。它们以相同的波形大小和累积次数设置同步运行。但是,每个通道的滤波器和阈值参数是单独设置的。ADQ-FWATD的框图如图1所示。

图1

a. 为了充分利用ADC的范围,可以在信号中加入模拟直流偏移。这样可以有效地将单极脉冲的动态范围扩大一倍。

b. 数字基线稳定器(DBS)是Teledyne SP Devices在脉冲数据系统中用于基线稳定的专有算法。DBS输出是一个受控的基线电平,设置在用户定义的22位精度值上。

c. 通用数据路径FIR滤波器,用于限制带宽和降低宽带噪声。

d. 用(c)作为抗混叠滤波器,跳过样本进行数据缩减或完全抽取。

e. 高级阈值操作是一种非线性噪声抑制,可以区分低于用户定义水平的样本。即使脉冲幅度与噪声具有相同的数量级,滤波器也可以对具有一定形状的样本序列进行复杂的提升。

f. 波形平均会积累大量的波形,通过重复测量进行随机噪声抑制。请注意,累加器将波形相加,划分则由用户在PC机上执行。

g. 无缝流式传输到主机,几乎提供了死区时间的免费采集

h. 为了实现更长的波形RL和更长的累积NA,可以在ADQAPI中进行第二部分的累积。分区算法决定当前用例是否需要在ADQAPI中进行积累。

i. 如果需要,用户可以在用户应用程序中使用更长的格式,如gint64,继续进行平均化。

j. 通过USB3.0或PCIe将数据传输到主机PC。

触发波形

波形是触发事件后的一组连续数据。在本文中,该数据集也称为记录。下面是用于触发波形的可用触发源。

内部触发源—使用内部参考时钟在数字转换器内部产生触发信号。默认情况下,内部触发器是自由运行的。内部触发器可以作为主外部设备在连接器TRIG上输出。

外部触发源—通过连接到前面板上连接器TRIG的外部信号触发设备。

软件触发源—软件触发功能在操作过程中实际用途有限。它在调试和系统设置过程中非常有用。

电平触发—输入信号的幅度决定了系统何时触发。因此,触发是由数据驱动的。

采用波形平均的系统最好是重复测量。触发既可以是从外部设备开始采集的外部触发,也可以是内部触发,其中ADQ通过连接器TRIG控制外部设备。在一些应用中,某些脉冲形状是值得关注的。数据驱动的电平触发可用于在重复脉冲上多次触发。

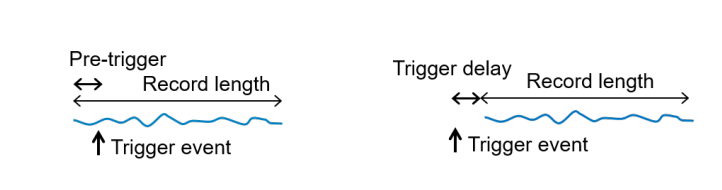

波形始终具有固定(用户定义)的长度RL,但用户可以自由选择波形的开始时间。相对于触发事件,波形的开始时间可以来回移动。设置预触发采样数的参数适用于关注触发事件之前的样本的应用。对于触发过早的应用,可以使用另一个参数来控制触发延迟。预触发和触发延迟如图2所示。请注意,预触发和触发延迟均不会影响记录长度。

图2 预触发和触发延迟的说明。用户可以自由选择波形的起始采样。

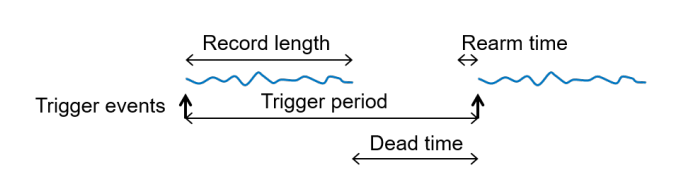

两条记录之间的时间称为死区时间。死区时间受重新设置时间(从最后一个波形采样到系统准备接受新的触发的时间段)的限制,同时也受数据传输到主机的速度的限制。死区时间和重启时间如图3所示。最小死区时间的数量级为几十纳秒。’

图3 触发期、重启时间和死机时间的说明。

在图3中,还显示了触发周期。如果触发周期

减少随机噪声和提高灵敏度的一个常用方法是重复多次测量,研究平均信号。这种方法可以减少非相关的噪声,增加相关的有用信号。波形平均的方法会产生大量的测量数据。为了减少主机的负载,FWATD在板载FPGA中加入了对实时波形累加的支持。

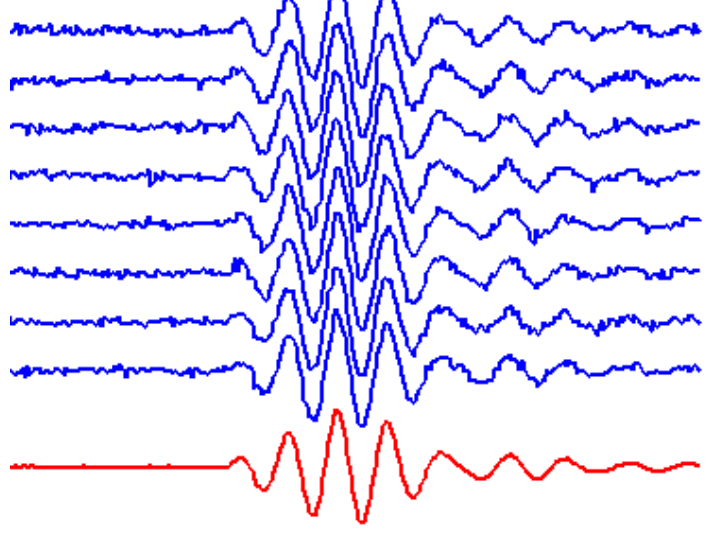

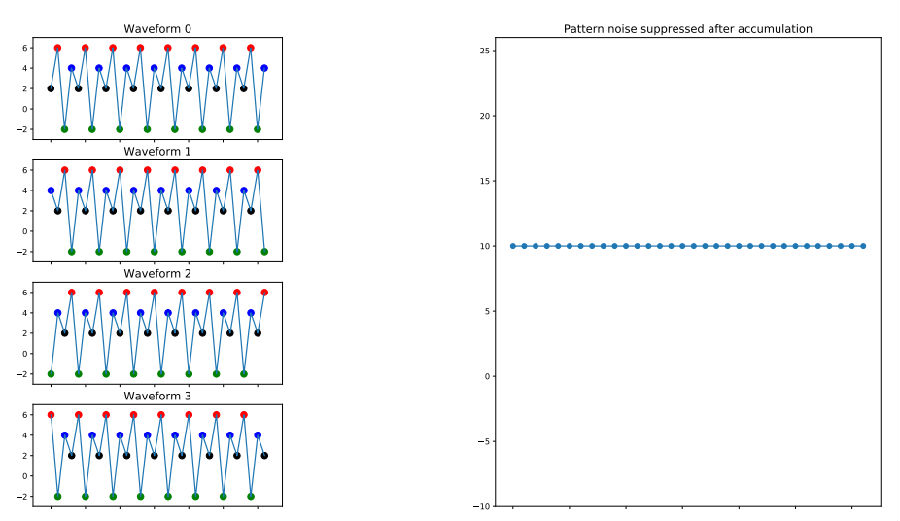

波形平均(WFA)是一个将波形相加的累加器。每个波形中的第一个样本与所有其他波形的第一个样本相加。根据定义,平均函数应该包含一个带有波形数NA的除法。然而,这种划分不适用于FPGA实现,因此留给用户在软件中执行。WFA的概念如图4所示。

图4 波形累积的图解。

当积累大量的波形时,任何系统性的信号都会受到影响,显得更加清晰。不仅对想要的信号产生影响,对相关噪声也是如此。这种相关噪声也称为模式噪声或系统噪声。模式噪声的主要来源是ADC内核的交织。其他模式噪声的来源是时钟,与触发频率相关。通常情况下,ADC的内置噪声抑制就足够了,但由于WFA的存在,其余的变化可能仍然是一个问题(因为它们的增益与所需信号的增益相同)。从而降低微弱信号的可见度,因此与模式噪声在同一范围内的信号在累积后也会被隐藏起来。

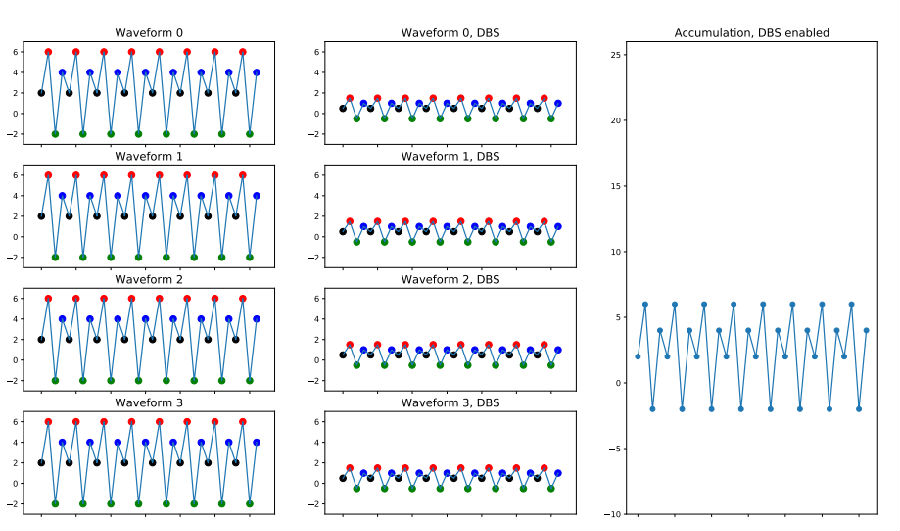

我们提供了三种处理系统噪声的方法,其中一种是DBS。另外两种方法是利用波形的触发来随机化系统噪声。虽然噪声仍然是系统性的,但它会因波形不同而不同,因此积累一些波形将随机化和抑制噪声,如图5,显示了理想的情况,其中触发位置平均分布在四个ADC内核上.这三种方法具有不同的质量,因此选择的方法取决于应用。表1总结了下面描述的方法的属性。

图5 模式噪声与所需信号的增益相同。重复模式是四个样本长

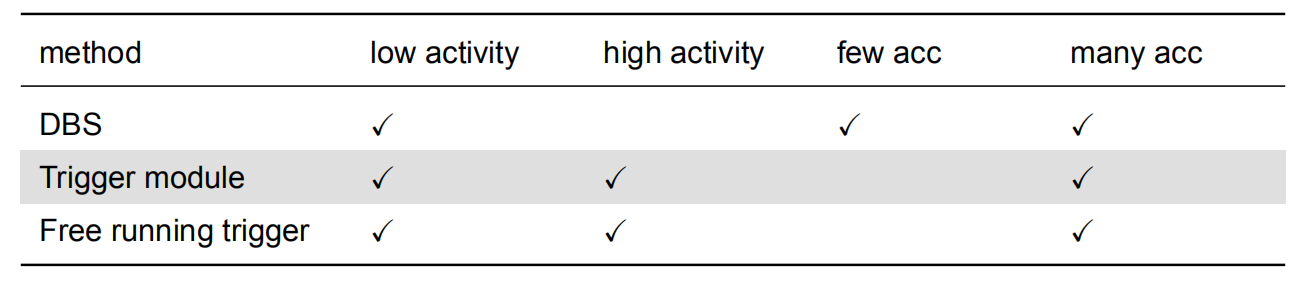

表1:模式噪声抑制方法在不同条件下效果最佳。选择的方法取决于当前应用程序的活动性高还是低,以及是否包含很多或很少的累积量 低活度意味着此处隔离的基线在一段时间占主导地位。

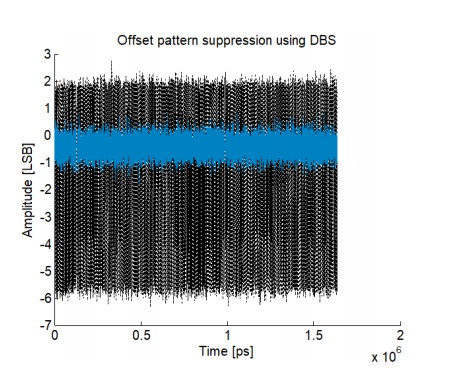

DBS —DBS通过从数据中估计偏移量并减去每个内核估计偏移量来消除模式噪声。图6显示了带有和不带有DBS的ADQ7的背景噪声。这种方法精度高,适用于低活度系统,也就是有明确基线的系统.因此,它的局限性在于需要一个基线才能正确估计偏移量。高活动输入信号(例如正弦波)会产生较差的结果。DBS的一个优点是它可以处理一条记录。如图7所示,不需要大量的累加即可获得良好的结果。

图6 来自ADQ7的背景噪声,有(蓝色)和没有(黑色)DBS。

图7 DBS对单个波形的模式噪声进行抑制,不需要积累就能获得良好的效果。

自由运行触发器— 拥有自由运行的触发器意味着它不与ADQ的采样时钟锁相,内部触发源默认为自由运行。使用自由运行触发来抑制模式噪声通常有利于大量累积。即使抑制水平不能保证(因为触发频率是不确定的),实现良好降噪的概率也会随着累积次数的增加而增加,NA。自由运行触发器的一个缺点是未锁定的触发器可能会涂抹短脉冲。

触发模块解决方案(附加的硬件选项)—触发模块是外部模式噪声抑制触发源,可以连接到TRIG(物理连接器)。触发频率确定为与ADQ的任何序列或时钟都不相关的数字。结果,通过累积抑制了图案噪声。与自由运行的触发相反,触发频率不是任意的而是固定的,该值使模式噪声随机化,从而通过累积将其抑制。触发模块是一个外部模式噪声抑制触发源,可以连接到TRIG(物理连接器)。触发频率被确定为一个与ADQ的任何序列或时钟无关的数字。因此,模式噪声是通过累积来抑制的。与自由运行的触发器相反,触发频率不是任意的而是固定的一个随机化模式噪声的值,从而通过累积来抑制它。