热搜关键词: PCIe高速数据采集卡RFSOC高速数据采集软件无线电平台VPX高速数据采集卡高速信号采集卡PCIe数据采集数字信号处理

✕

1、采集系统整体规格

系统采用标准的6U VPX 架构,包括如下几个部分:

1.采集模块,集成8通道 14bit 500MSPS采集,标准VPX 6U尺寸卡。

2.板载高速存储器,每通道支持512Msamples采样点存储。

3.时钟,触发同步模块,同步各个机箱中各个模块时钟。

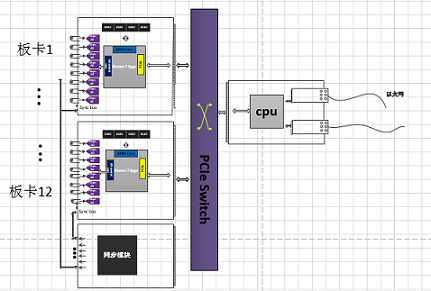

4.标准6U 14槽VPX系统,包括6U 14槽背板,控制器以及机箱,控制器模块可以通过以太网口将各通道的采集数据传输到上位机进行数据处理。

5.同步采集校准系统。统一的基准时钟和触发信号分发。

6.上位主控计算机,通过千兆以太网控制各个采集系统,并从采集系统中读取每通道的采集数据。

系统具有以下特点:

1.采用标准6U VPX机箱,整个系统紧凑,符合工业级温度工作范围,-40C°至85C°。

2.每个机箱可以插入12块采集板,每块采集板包括8通道500MSPS,14bit采样,和高速存储系统;一个机箱总共支持90通道采集。

3.每个机箱采用独立的时钟/触发控制模块,进行时钟和触发信号的分发,采用星形拓扑结构,通过背板的高速互连线进行等延迟的统一分发时钟和触发信号。

4.同步校正系统统一放送基准时钟和触发信号。

5.通过自定义背板连接信号,增加了系统的紧凑性,大量减少了连接线。

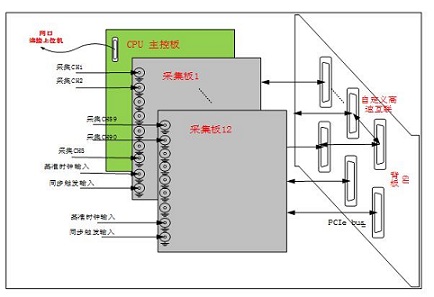

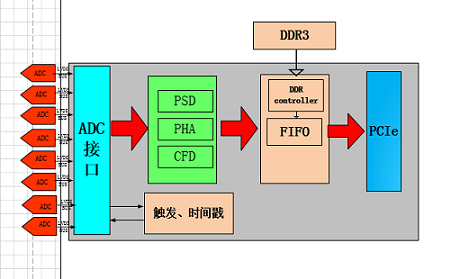

系统实现框图如下:

数据传输原理图:

2、采集模块介绍

每个采集系统有如下部分组成:

1、12块采集模块,每块采集模块集成8通道500MSPS 14bit ADC,每通道储存空间至少为512Msamples。

2、1块同步时钟/触发模块,接收系统基准时钟和触发控制信号,以及校准信号。

3、主控模块,负责接收上位机的控制命令以及上传采集数据。

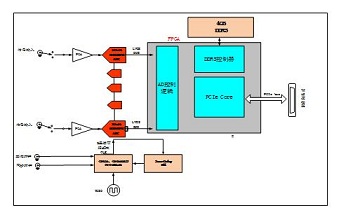

采集模块的实现原理如下:

采集模块技术指标如下:

ADC输出位数 :14bit,采样率500MSPS

有效位数(ENOB)(typ.):8.1bit

模拟带宽:300MHz

输入阻抗:50 欧,AC/DC藕合/SMA

满量程输入量程:700mVpp或1Vpp

时钟:支持板载时钟或外时钟

触发:支持软件触发或外触发

3、专用于核物理的采集功能:

采集数据并行处理逻辑:

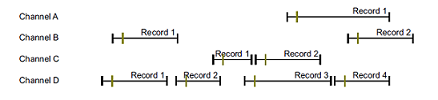

1、每个通道独立工作,通过脉冲电平触发,单次采集时间可设置在1us左右。

时间戳(time-stamp)功能:

时间戳选项将信号触发事件开始的时间记录于一个额外的内存空间。时间戳是对应的是每次采集开始的时间信息,其与外部无线时钟或GPS时钟同步,采用这一选项使得采集模块可准确记录每次采集的发生时间,并且不同位置的采集系统之间存在一个精确的时间对应关系,有利于实现对信号的记录、分析。

3、每个通道完成三种算法:

a, 恒比定时(CFD)

恒比定时是具有恒定触发比的时检电路,是为了解决过零定时中触发比不能

调节到佳值而发展起来的一种定时方法。

设输入信号气Vinput=Af (t) , A为幅度。Vth =p*A为触发阈值,则过阈值时时间取决于下式的解:

Af(t)一pA=0

由上式可见,f(t)为任意函数,t的解与A无关。

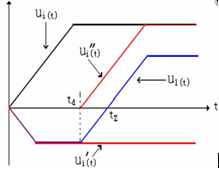

恒比定时的实现方法如下图所示:

b , 脉冲形状甄别(PSD)

(1),积分(CI)。

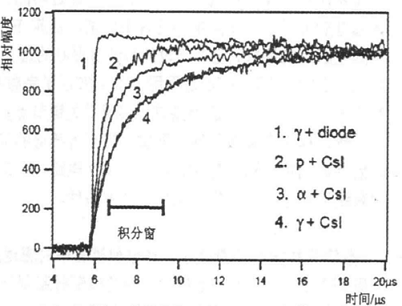

如下图所示,不同类型射线作用输出的核脉冲信号在特定窗口内的积分面积相对于脉冲幅度有明显差异,这种粒子区分方法适用于低幅度脉冲信号甄别,并具有较宽的动态范围。

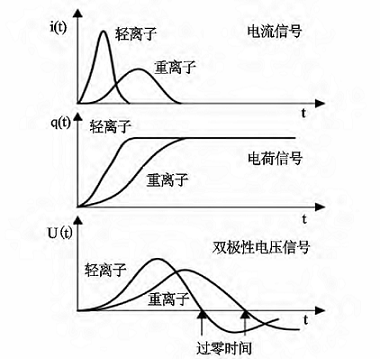

(2),过零时间检测(ZLEplus)。

如下图 所示,较重的粒子产生的电流脉冲持续时间较长,幅值较低,电荷上升时间较长,过零时间也较大。

(3)脉冲高度分析(PHA)

脉冲高度分析是核物理中的一种常用测试方法,即利用探测器接收脉冲,并分析计算不同粒子的脉冲高度,并保存通达或寄存器中每个高度的脉冲数量,以助于后面的谱分析。

(4)微分。

不同入射荷电粒子在探测器中输出的脉冲信号是不同的, 其主要表现在脉冲前沿上。对具有一定上升时间的脉冲信号进行双微分, 则双微分后的脉冲与零电平相交产生一个过零点, 它只与脉冲信号前沿时间有关。通过对脉冲前沿起始点与过零点时间的测量, 则可对入射荷电粒子进行分辨。该方法实质上是将探测器输出脉冲前沿的差别转化为脉冲起始时刻与过零点间时间上的差别, 并将时间差别通过TAC转换来实现对入射荷电粒子的分辨。

(5)脉冲前沿拾取。

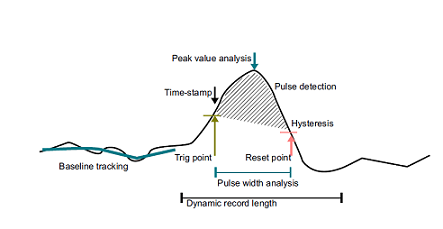

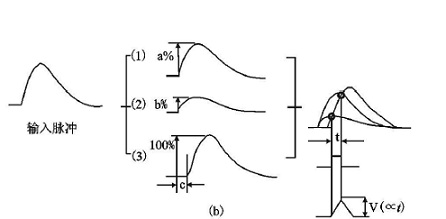

脉冲前沿拾取方法的原理如下图:

采集后输出信号分为三路, 路衰减为a%, 第二路衰减为b%, 第三路脉冲不变并延迟一段时间τ0 , 将二三路脉冲进行混合比较, 这两路脉冲有一个交点, 将该点作为下拾取点, 送到混合器触发脉冲作为触发开始;一三路混合比较, 脉冲交点作为上拾取点, 作为触发结束, 这样输出的脉宽时间也就对应着脉冲前沿拾取份额, 份额大小由对脉冲衰减的状态确定, 即由a%到b%之间的差值决定。在固定的幅度范围内, 脉冲上升快的需要时间短、脉冲上升慢的需要时间长, 通过测量时间长短进行粒子分辨,所以可以根据实际需要选择佳分辨的拾取时间。

这种方法只对探测器输出的脉冲前沿进行比较, 不涉及脉冲信号幅度。而且该种拾取是自身比较的拾取, 可大大减少外来因素对探测器脉冲影响而造成的分辨变差。

注释:

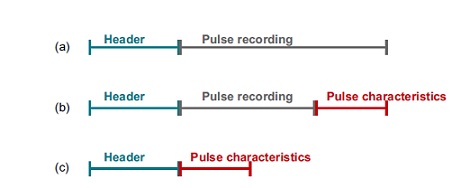

a,存储采集数据和时间戳等

b,在存储采集数据和时间戳的同时,尾部增加脉冲特征数据,如峰值、CFD、PHA、PSD。

c,只存储时间戳和脉冲特征分析数据,如峰值、PSD、CFD、PHA、不存储采集数据以节省空间。

4、多通道同步采集解决方案

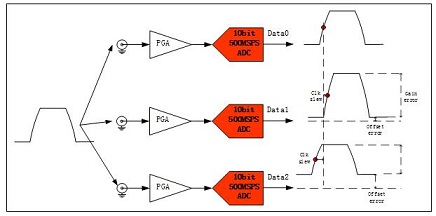

首先要保证多通道的时钟严格同步以及每通道的模拟电路以及每个ADC的工作状态一致性。在输入一个脉冲信号时,多通道系统有如下误差,如下图所示:

多个通道的采集误差主要由模拟电路以及不同ADC芯片的clk slew,gain error以及offset error组成。尽管我们在设计硬件电路以及PCB设计会尽量考虑以上问题,如同源的时钟分布以及相同的走线;多个ADC公用精准的外部参考电压源等等,但不幸的是,这些设计改进并不能完全消除这些由模拟器件本身的固有特性引起的误差,这些误差是随机的,也随温度变化而变化的。

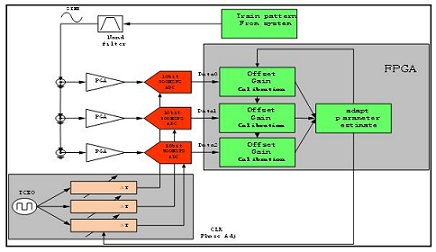

因此,动态校正电路以及自适应的数字后补偿算法是必不可少的解决方案。

校正功能有校正电路和FPGA算法部分组成,校正电路由高精度低速DAC,参考源,滤波器和时钟相位微调芯片组成。FPGA算法核心为参数估计自适应算法和校正参数逻辑组成。校正目标为设置一个基准通道,其他几个通道的时钟相位以及gain和offset向该基准通道标定。该方法不能校准每通道ADC的绝对精度,而只是每通道的个参数一致,这对测量每通道采集数据的相对相位是足够了!

校准信号为A*sin(ω*t+φ)+B;

CH0采到的信号为A0*sin(ω*t+φ0)+B0;

CH1采到的信号为A1*sin(ω*t+φ1)+B1;

`

`

`

CHn采到的信号为An*sin(ω*t+φn)+Bn;

通过迭代法解线性方程组,当方程收敛时,分别能得到每个通道的参数,通过计算每个通道的同基准误差,来调节clk phase 以及gain和offset来后是n个通道工作一致。Clk的phase通过专业的时钟调节芯片来进行调节。

同步时钟的传输和Clock jitter的消除:

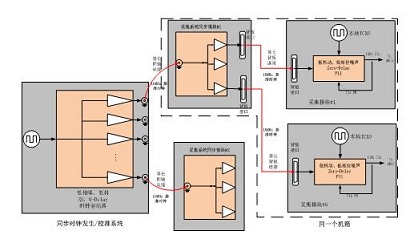

虽然有自适应校正来校正clk的传输相对延迟,但在电路设计时也要保证clk的小相对传输延迟和自身的clockjitter。对于整个多通道采集系统,时钟信号传输如下图所示:

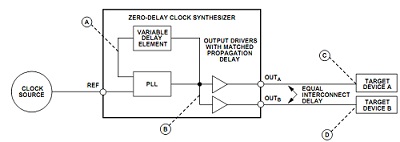

在所有传输过程中,均使用等长的传输线连接,基准时钟为10MHz。采用低频的基准时钟有助于减少干扰和传输中时钟的jitter。在采集模块及ADC输入信号端,我们采用zero delay 时钟发生器进行基准时钟和每个ADC采集时钟的相位同步,其zero delay pll如下图所示:

通过自动调节芯片内部的延迟来达到输出时钟和参考时钟的相位一致性。

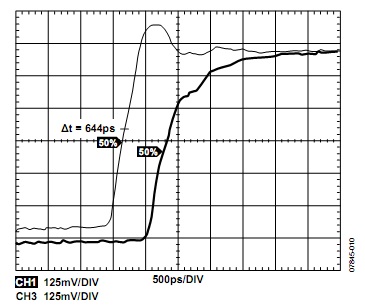

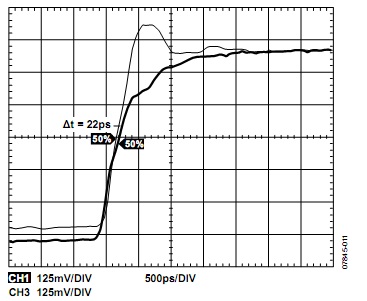

没有进行zero delay补偿的时钟输入/输出相位误差约为664ps,这个误差是一个范围,可能在0-644ps中随机出现!经过 zero delay补偿的相位误差如下图:

对于clock jitter的消除:

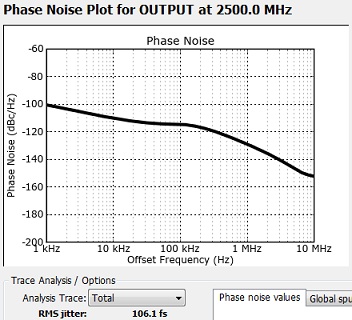

该方案中采用超低相位噪声的恒温晶体以及业内顶级的 Jitter cleaning CLK Generator芯片来保证clock的稳定性,Clock jitter的消除以及极低的Phase noise。

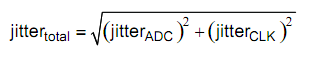

对于时钟芯片的选择,也是基于同样的考虑,集成高精度高稳定的VCO,具有Jitter cleaning功能和clk phase adj功能。通常,jitter由ADC本身的jitter和CLK jitter组成,各自的RMS再组成总jitter的RMS:

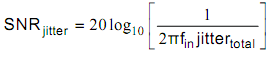

总jitter的RMS会在采集系统中产生白噪声,其关系如下:

采集系统的总 ![]()

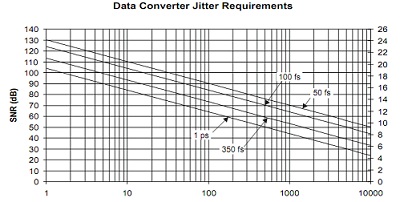

采用本时钟解决方案,其总的clock jitter在系统中完全能做到<350ps< span="">。在忽略信号noise ,DNL等情况下,fin和clock jitter有如下关系:

小型化的恒温晶体加超低相位噪声时钟发生器,实现2.5G时钟输出时的抖动约100fs:

5、系统电源干扰的解决方案

1.电源抑制(PSR)是采集系统的比较重要的指标,高的PSR能拟制电源上的CML共模噪声,该方案中选用的ADC具有80dB以上的电源拟制比。

3.合理的PCB布线和接地

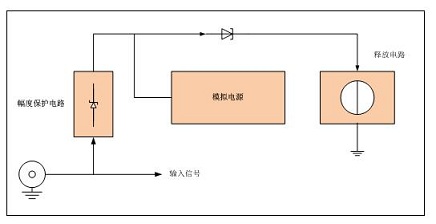

输入保护电路:

由于输入端口可能有很大的高电压冲击需要对输入端口进行限幅设计,并且限幅度后,能量能快速泄放掉,及输入端口的电路没有残余的电荷存在,以至于影响正常的数据采集。

该电路以下几部分组成:

1.幅度保护电路(含瞬态保护二极管)。

2.隧道电路,由于许多模拟电源输出端只能输出电流,不能输入电流(灌电流),所以需要快速的隧道电路建立快速的灌电流通路。

3.释放电路,通过开启近似理想的电源,迅速释放电流到地。

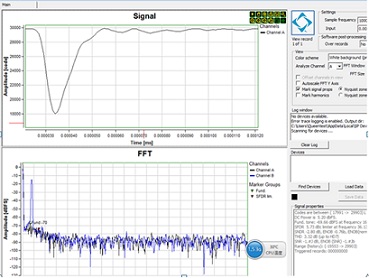

系统软件包括应用软件,二次开发API函数。应用软件,具有虚拟示波器功能,方便设置硬件,读取/保存数据以及波形显示/频谱分析功能。

1、其功能和界面如下所示:

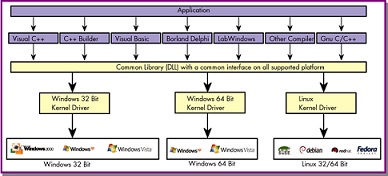

2、二次开发API函数:

我们提供丰富的接口函数和系统主要功能的例程,支持C/C++,labview以及Matlab环境下的二次程序开发。