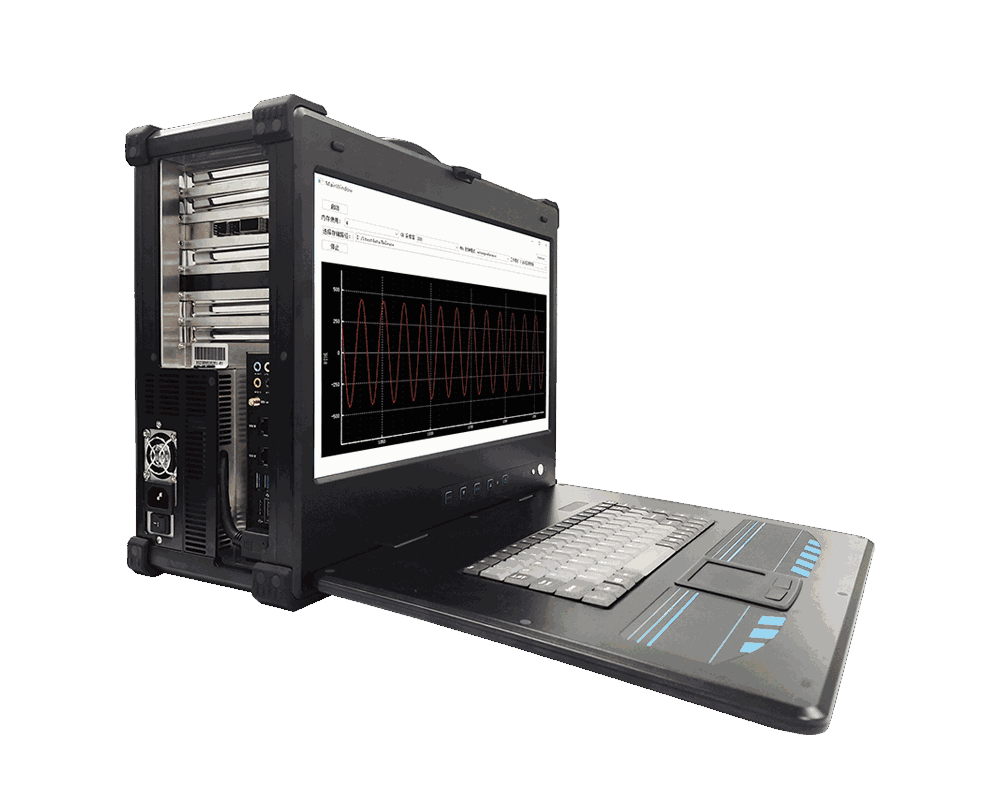

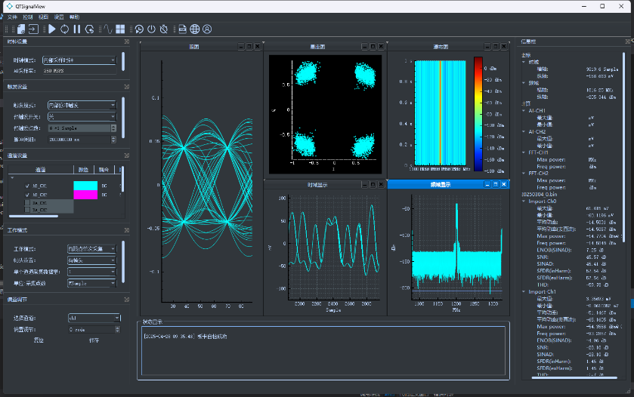

同步控制系统方案

系统规格:

系统主要完成同步触发和时间信息的同步放送,以及接收功能。

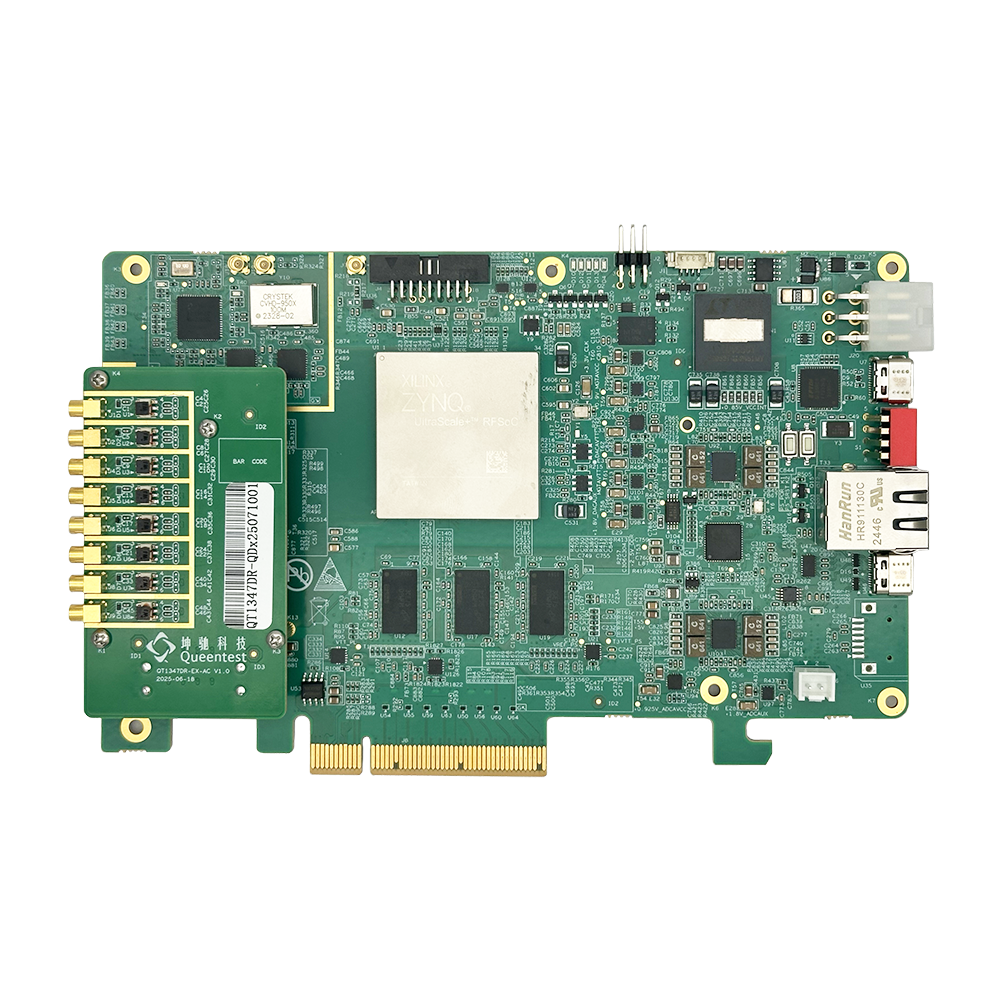

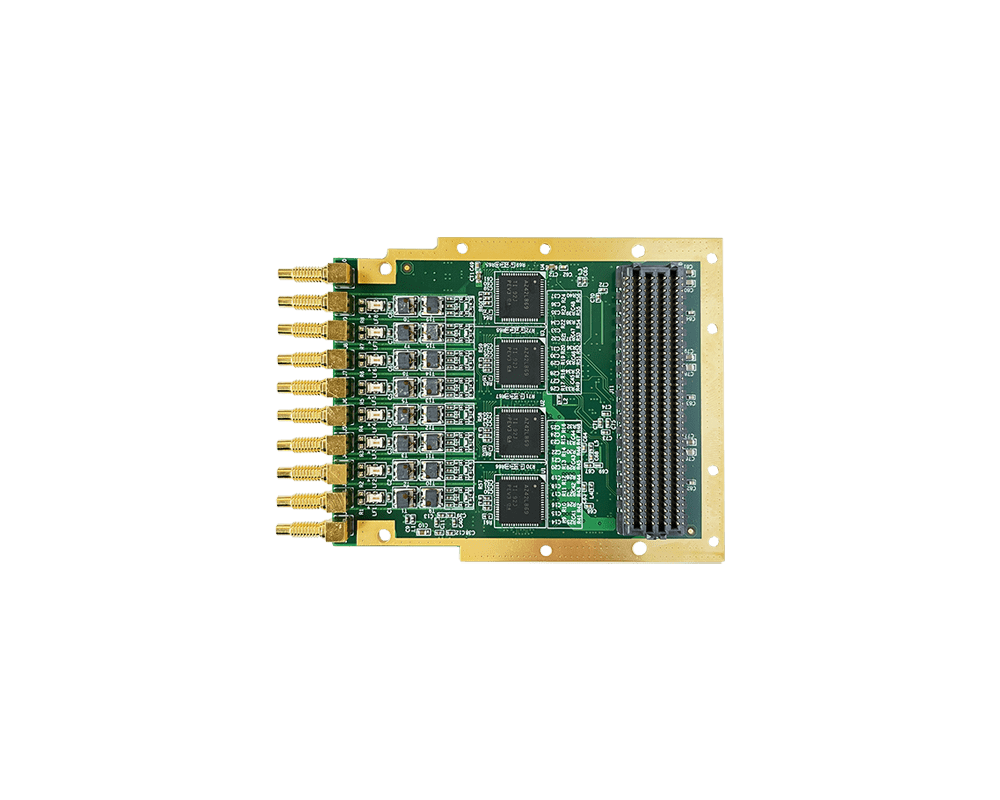

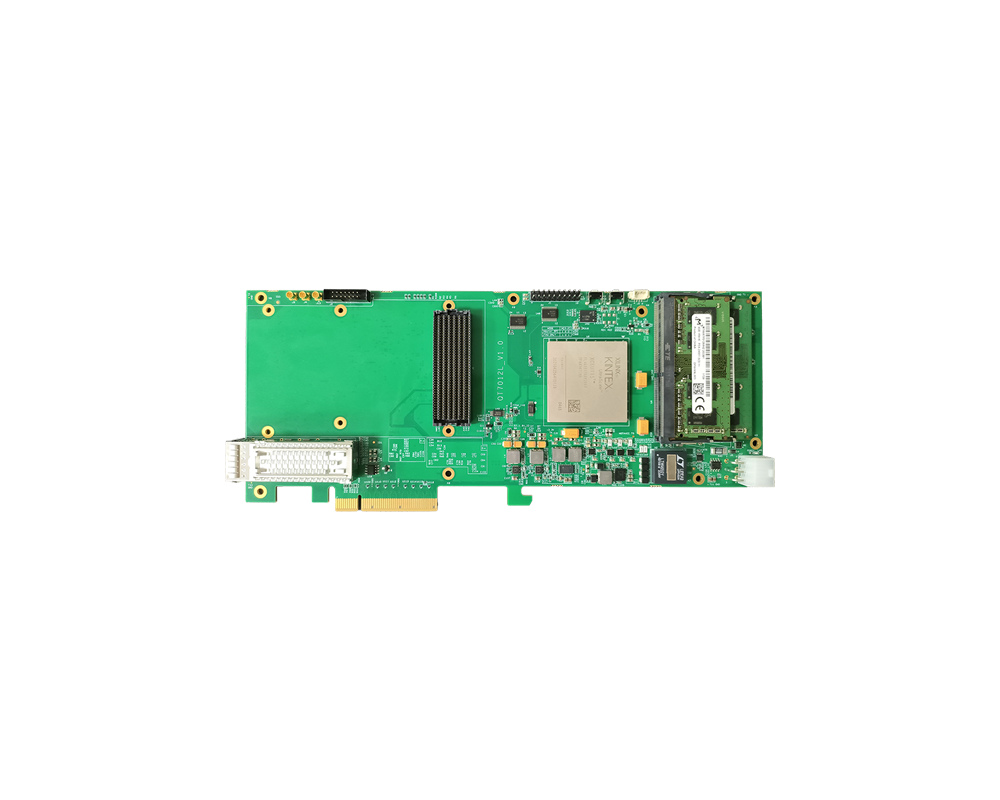

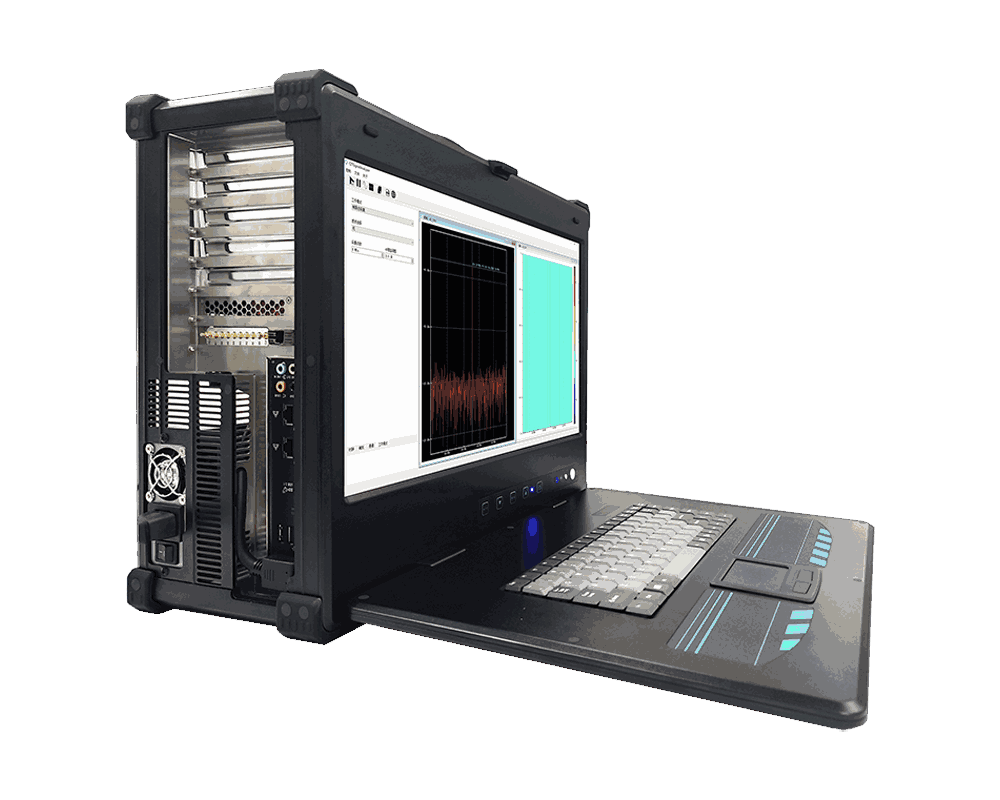

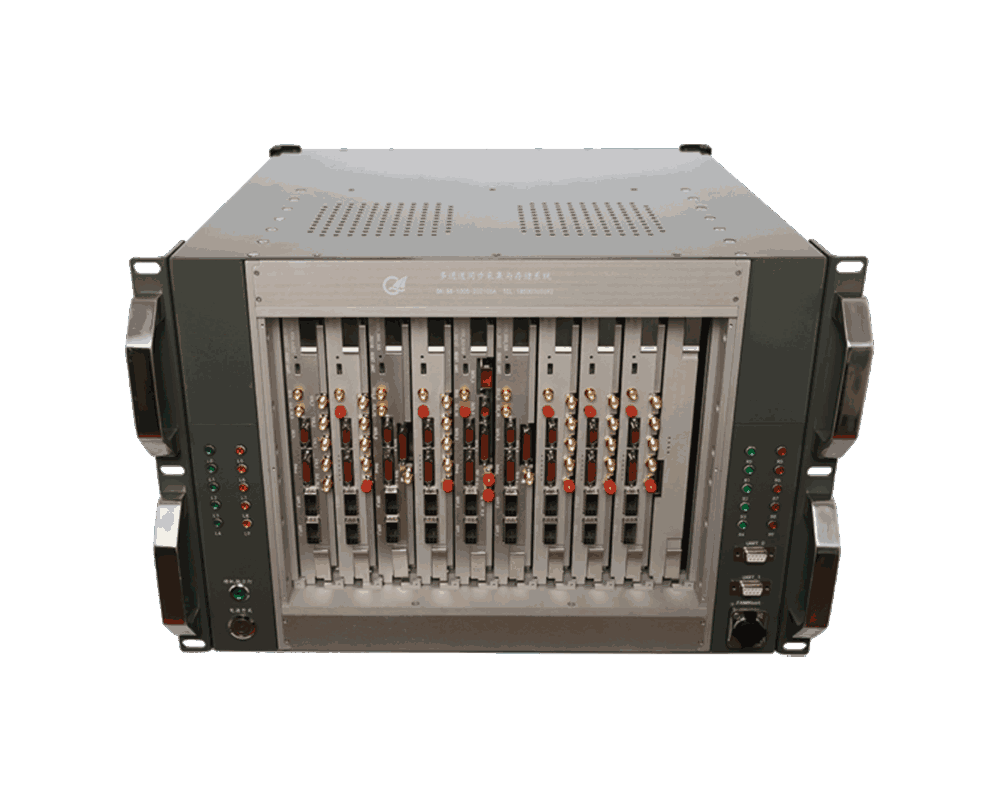

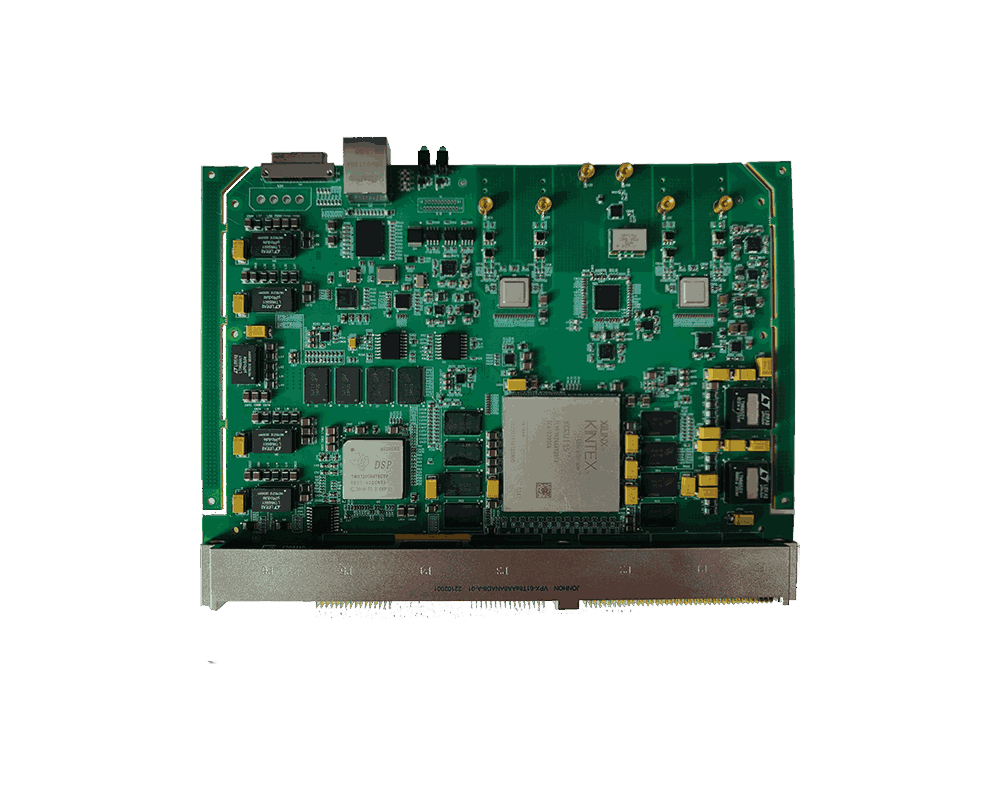

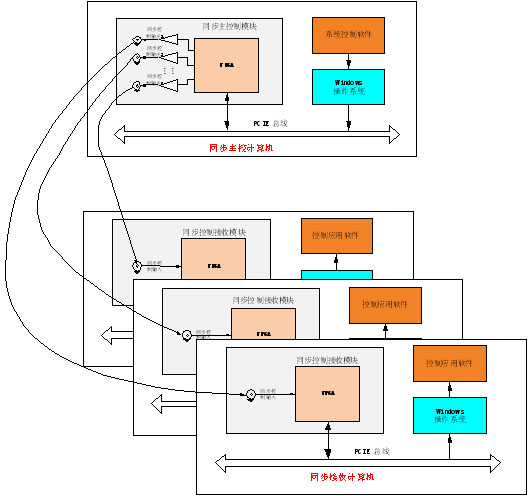

系统由同步主控模块和同步接收模块以及控制软件和FPGA逻辑构成,完成多个不同设备的同步控制功能。

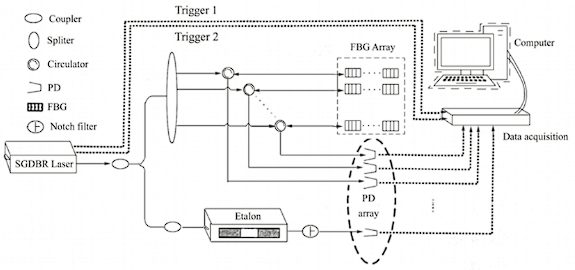

系统实现原理如下:

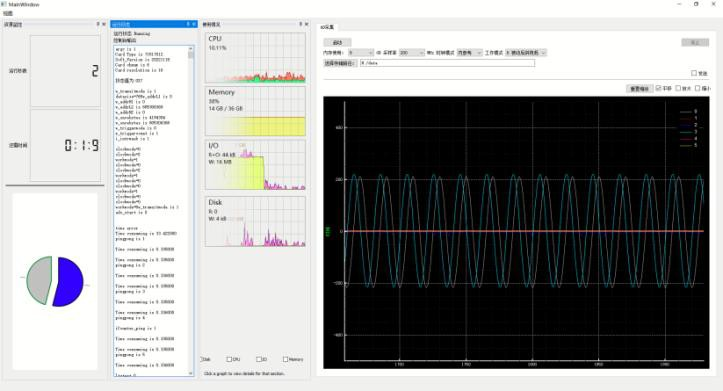

整个系统由一块主控同步控制模块和几个同步控制接收模块(数量由应用需要定)已经总体同步控制软件组成。

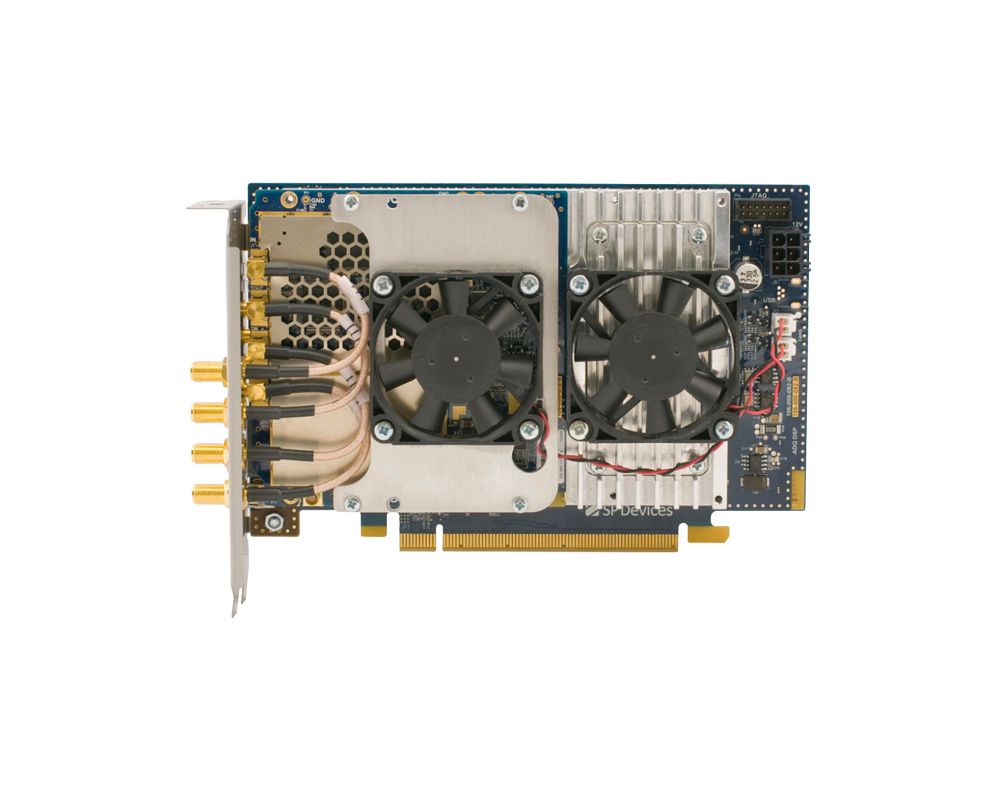

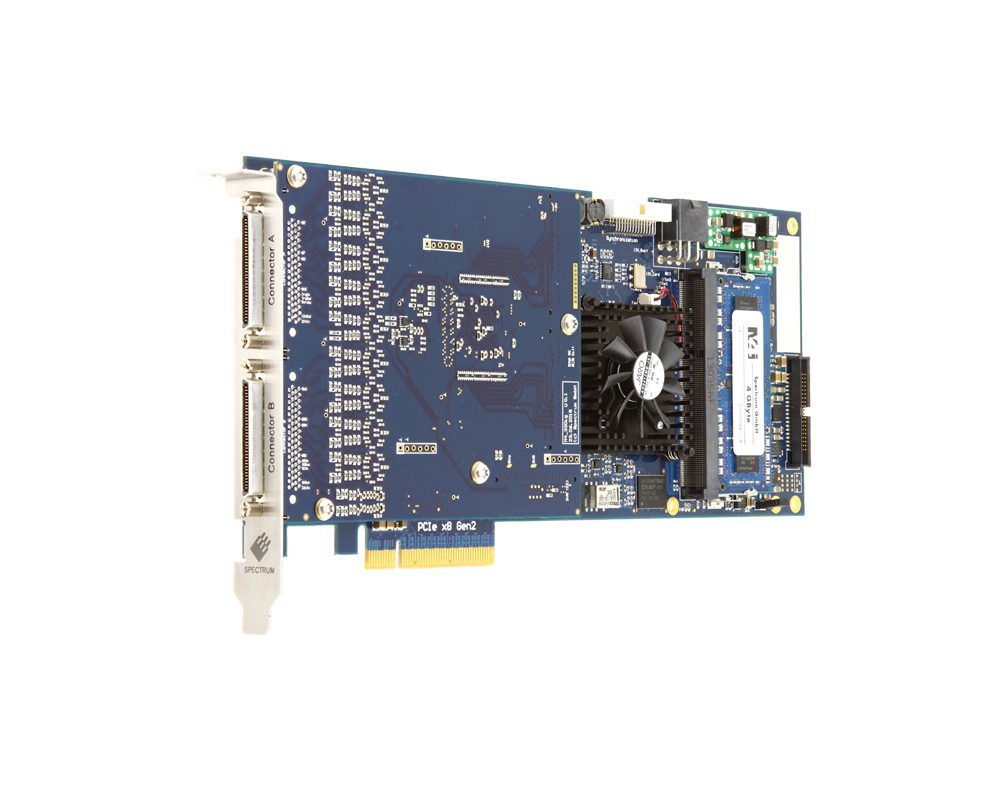

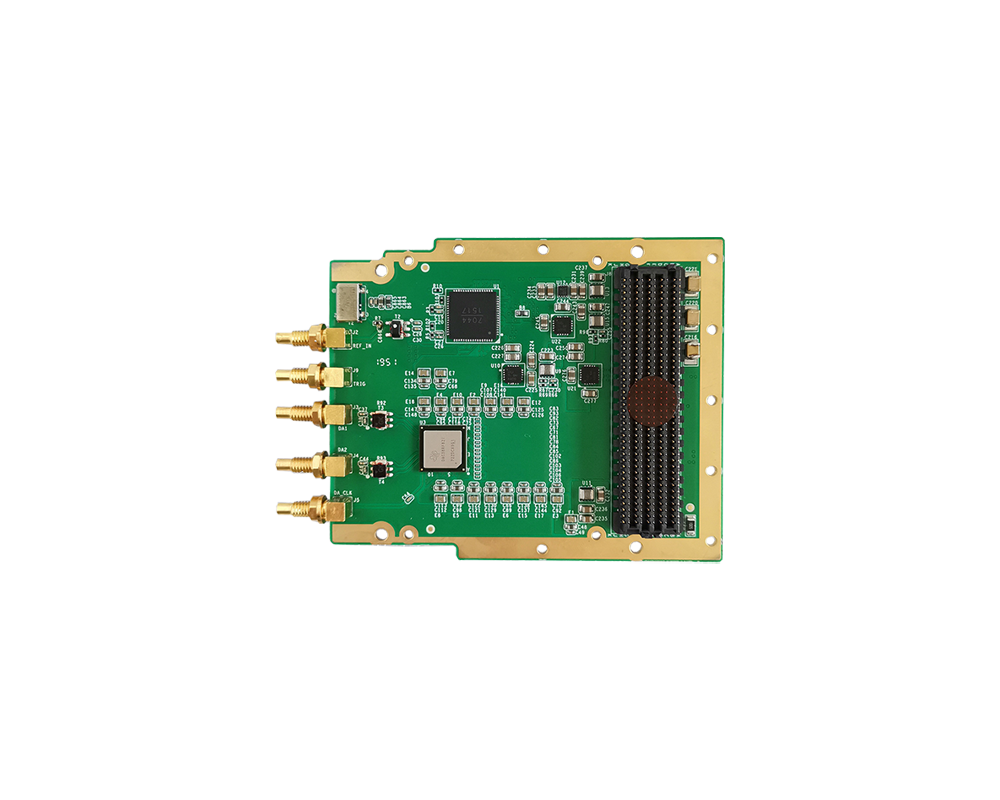

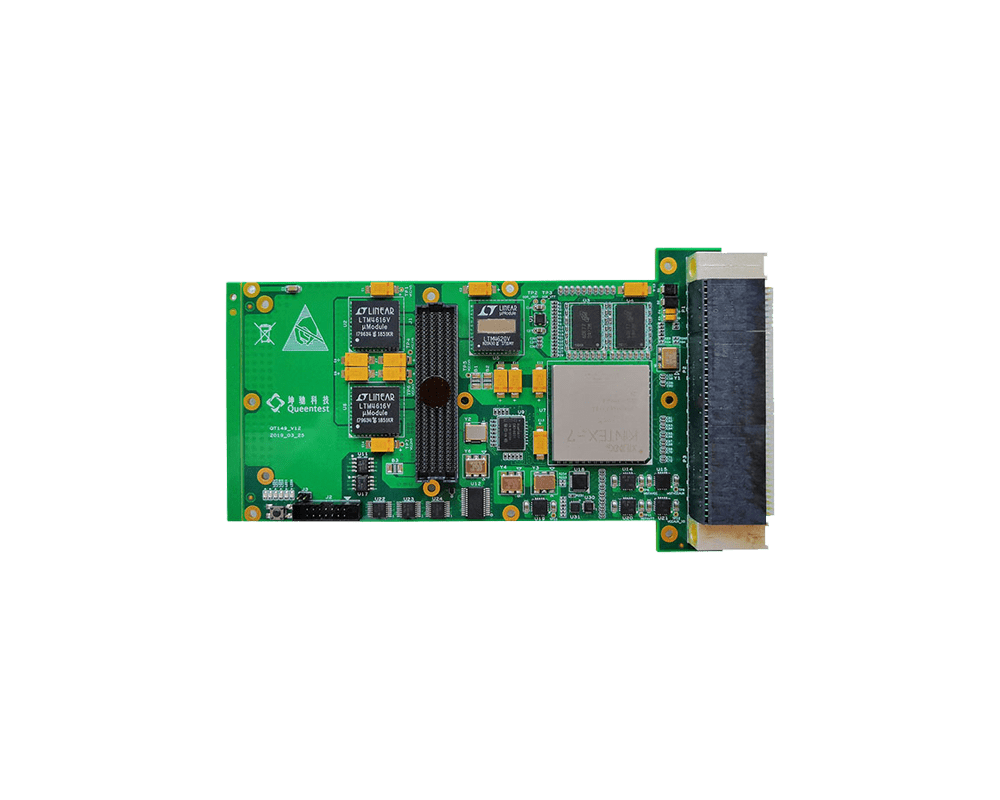

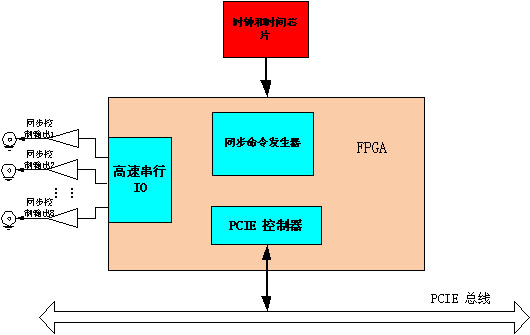

主控同步模块通过PCIE总线接收主控软件的控制命令,通过板载的FPGA控制时钟芯片和自身硬件逻辑,向各个同步接收卡发送同步和时间命令。通信协议由系统事先制定好,为了远距离传输命令,控制接口采用高速串行接口连接。

实现原理框图如下:

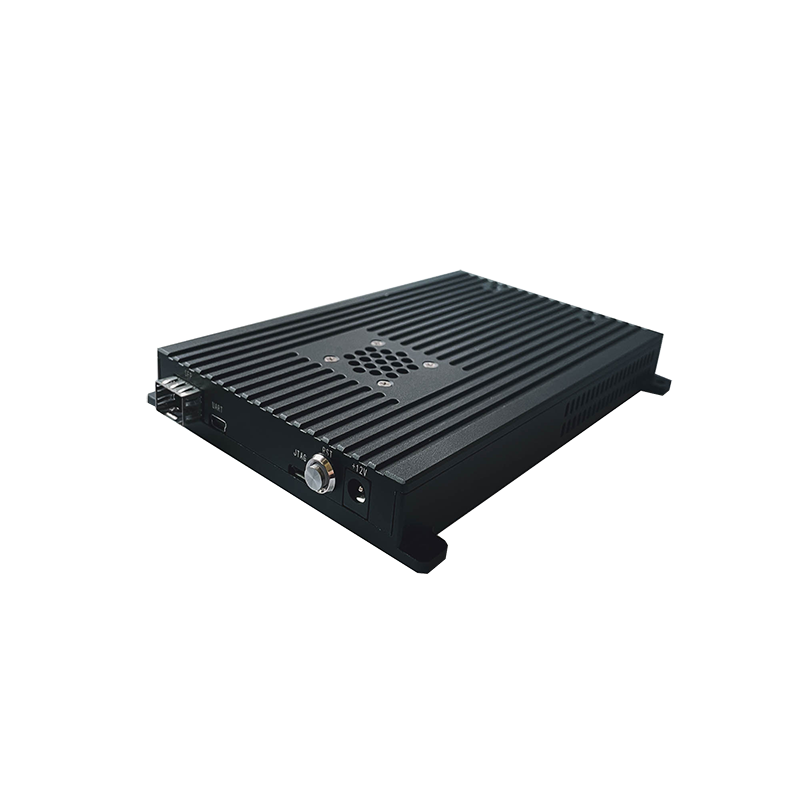

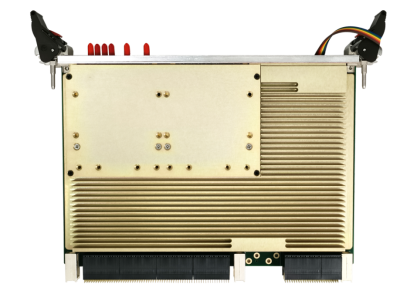

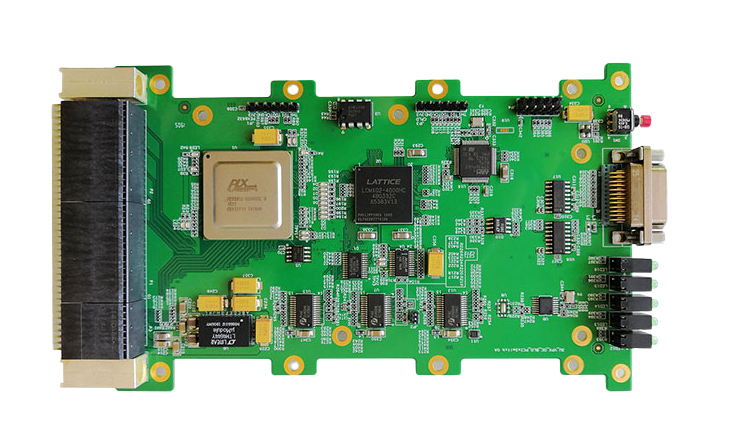

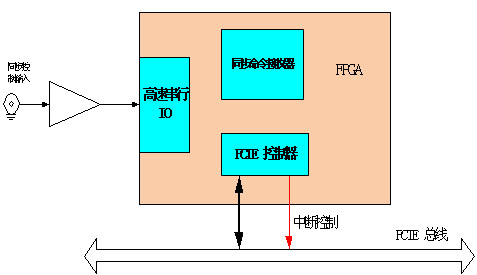

同步接收模块通过高速串行总线接收到主控模块的同步命令后,通过PCIE总线向系统申报中断,系统软件接收到中断申请后控制本地采集器开始工作,同时接收来自主控模块的时间信息,将当前采集数据打入时间标签。

实现原理框图如下:

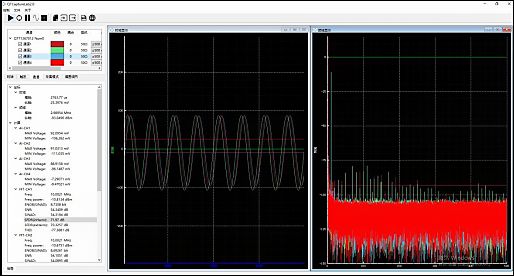

关于软件控制:应用软件结合高速IO,对外部事件快速响应,以大化的满足该方案的用户级应用响应;通过优化,用户级应用程序对外部事件(中断)的响应时间确保在1ms内。

同时该模块支持GPS定时功能

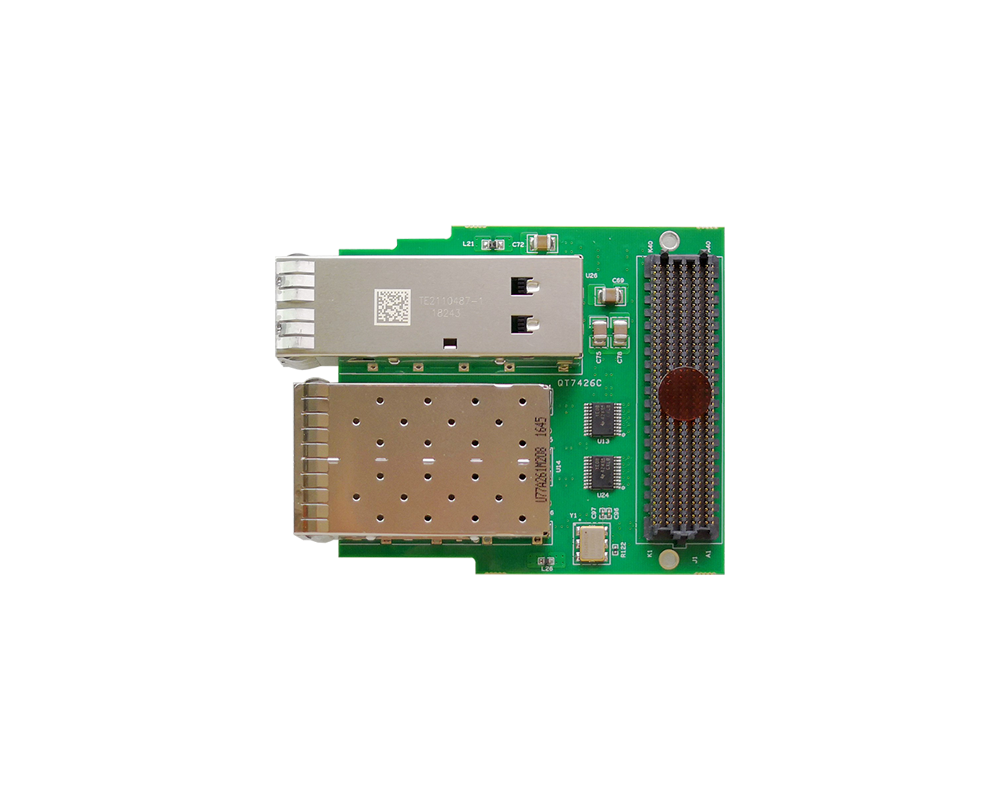

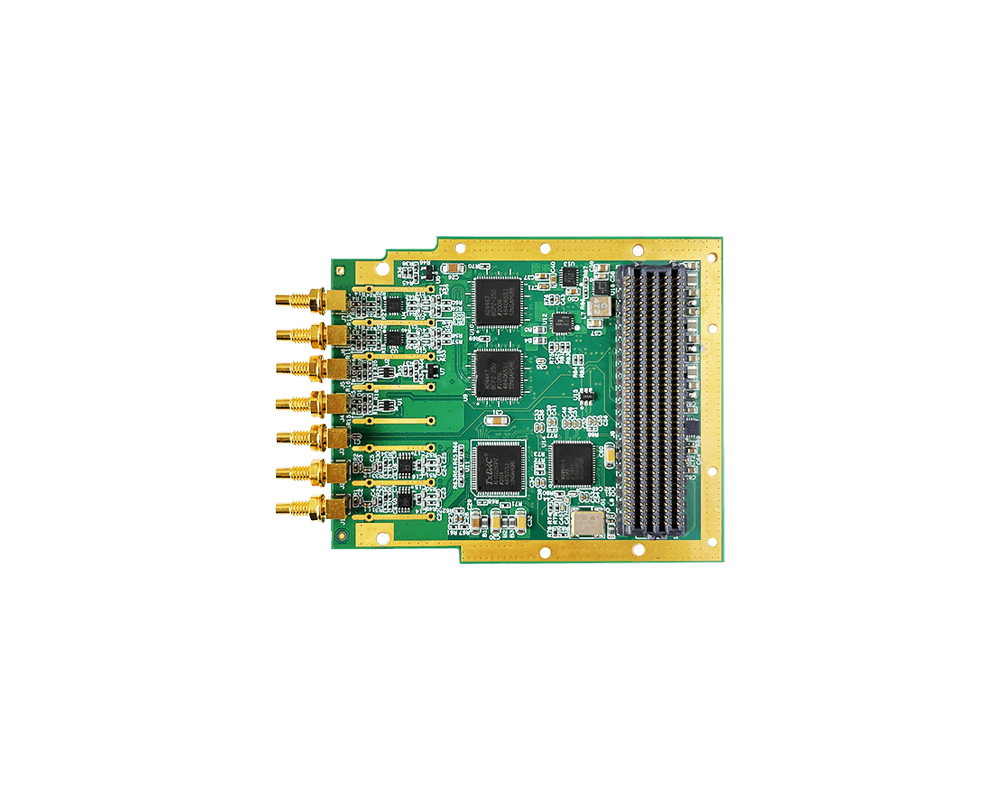

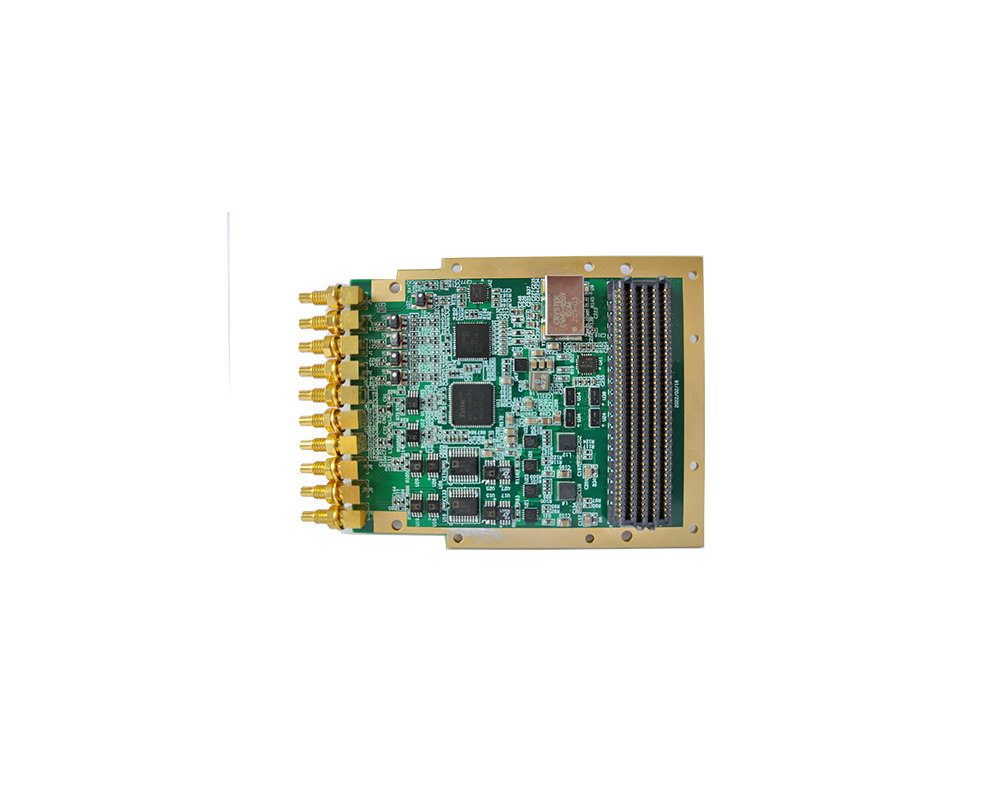

相关产品