- 方案概述

- 相关产品

- 联系我们

S波段收发信机方案设计

S波段收发信机方案设计

1、收发信机功能

1)无线通信功能,通过天线发射已调制射频信号,通过天线接收调制信号,并解调出信码。

2)以FPGA+DSP通用硬件平台,实现多种调制信号产生算法验证平台,如信道编码、交织、调制星座映射、插值及滤波算法等。

3)以FPGA+DSP硬件平台,能够完成多种解调算法验证,如载波同步、码同步、数字滤波等算法。

2、收发信机技术指标

发信机

1)工作频率:2.8GHz

2)输出功率:-60-20dbm

3)功率控制步进:≤1dB

4)邻道功率抑制:≥dB

5)调制制式:BPSK、QPSK、QAM、2FSK等

6)基带码速率:700Kbps

7)中频:25MHz

8)带宽:1.5MHz

9)本振输出频率:300MHz、2475MHz

10)本振信号相噪:≤-96dBc/Hz@1k(2.8GHz)

11)本振信号杂散:≤-55dBc(非谐波)

收信机

1)射频频率:2.8GHz

2)接收灵敏度:≥-90dBm

3)功率动态范围:90dB,自动增益控制

4)解调制式:BPSK、QPSK、QAM、2FSK等

5)中频:25MHz

6)带宽:1.5MHz

7)本振:300MHz、2475MHz

8)本振信号相噪:≤-100dBc/Hz@1k(1GHz)

9)本振信号杂散:≤-55dBc(非谐波)

10)中频大输出功率:≤5dBm

11)误码率:1×10-4(符号信噪比12dB)

3、收发信机总体方案设计

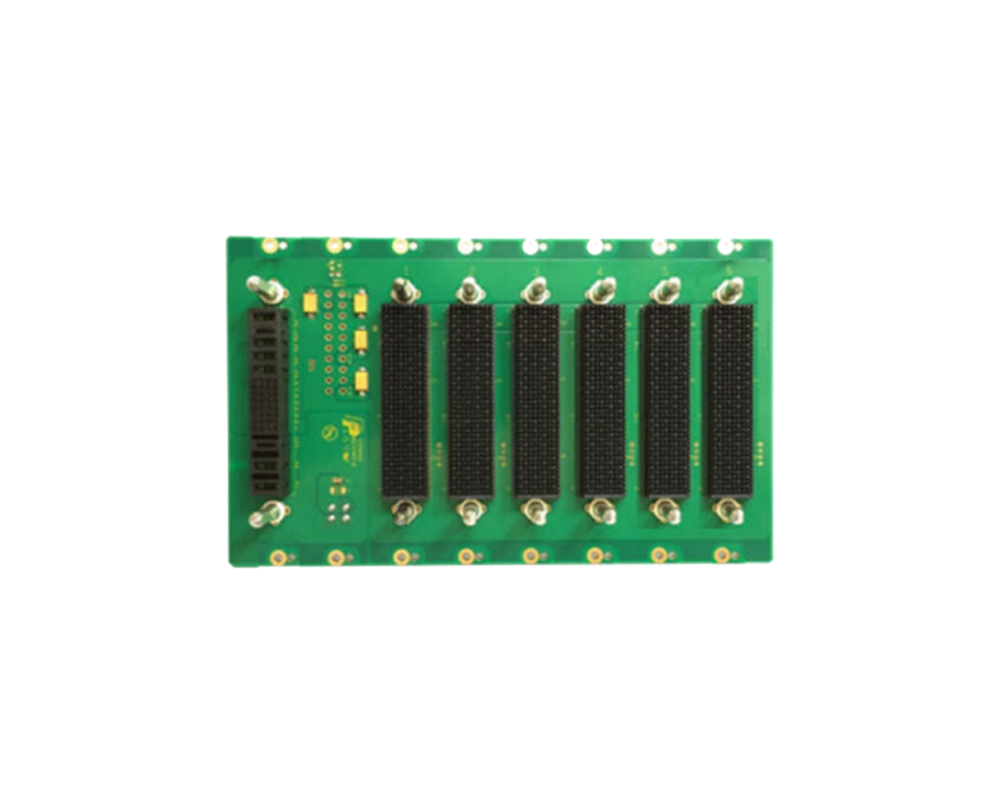

3.1收发信机组成

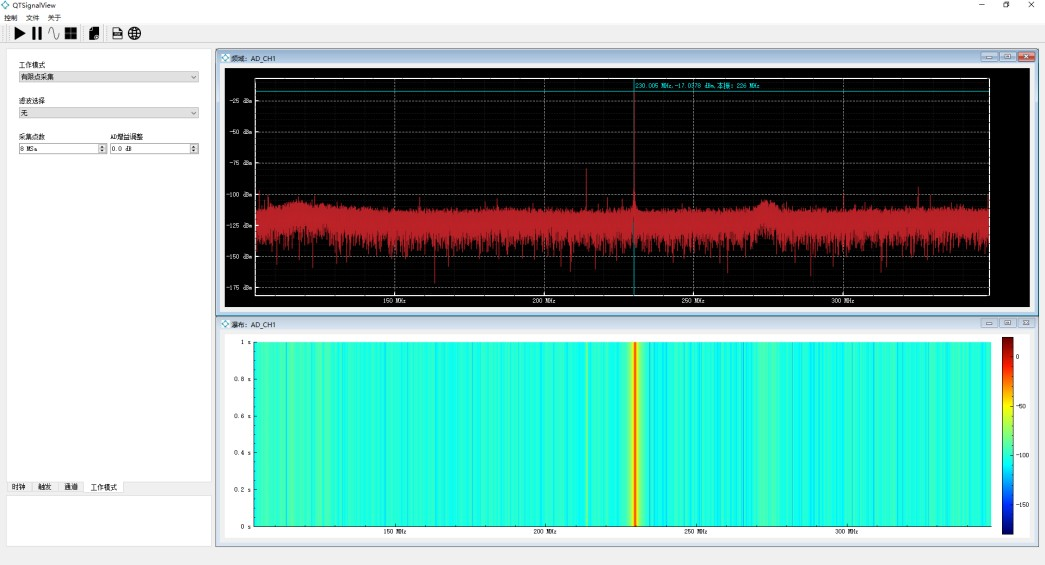

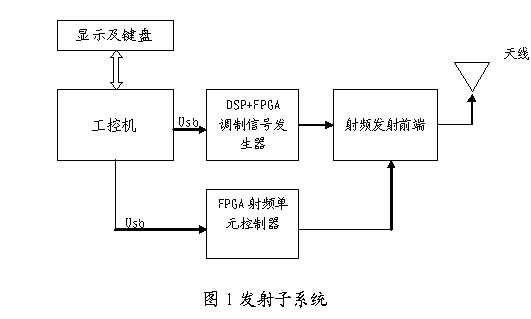

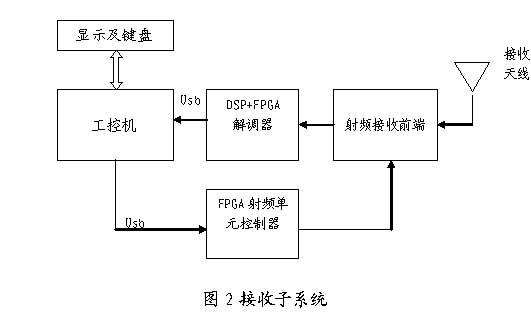

软件无线电通信验证系统主要包括发信机和收信机两个子系统,由系统控制器、系统显示器键盘、DSP+FPGA调制信号发生器、射频发射前端、发射天线组成发信机子系统;由系统控制器、系统显示器键盘、接收天线、射频接收前端、DSP+FPGA数字解调器组成收信机子系统,系统组成框图如图1、2所示:

图1发射子系统

图2接收子系统

3.2发射子系统设计

这里主要对发射子系统中关键模块DSP+FPGA调制信号发生器、射频发射前端及控制进行设计说明。

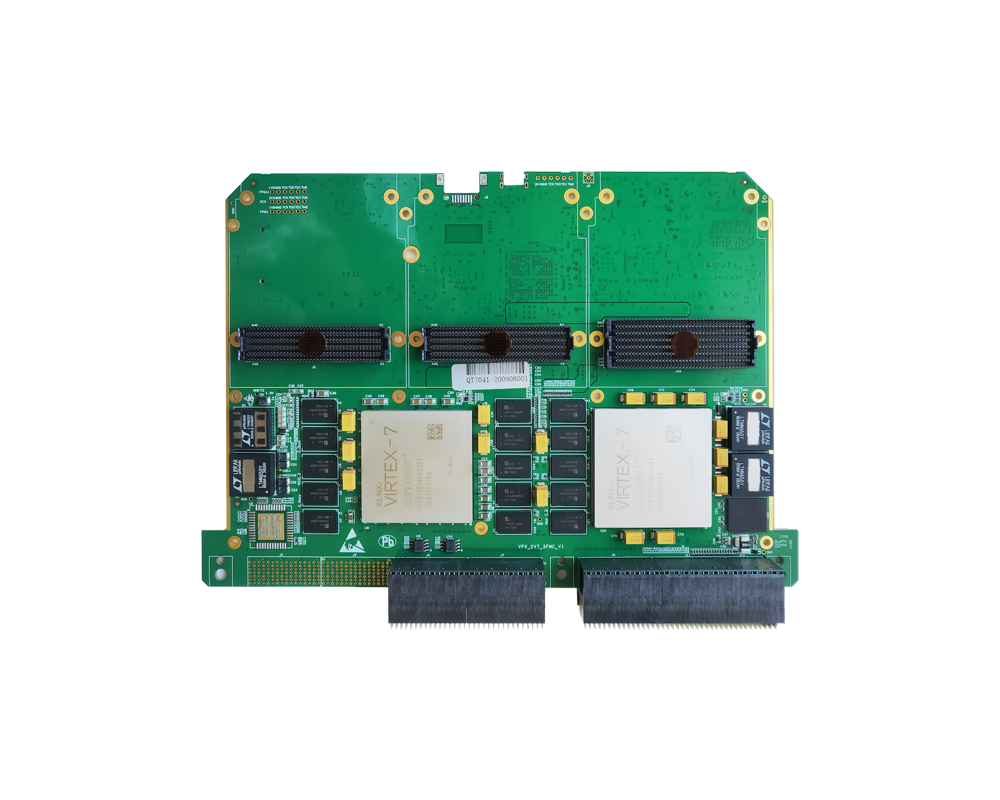

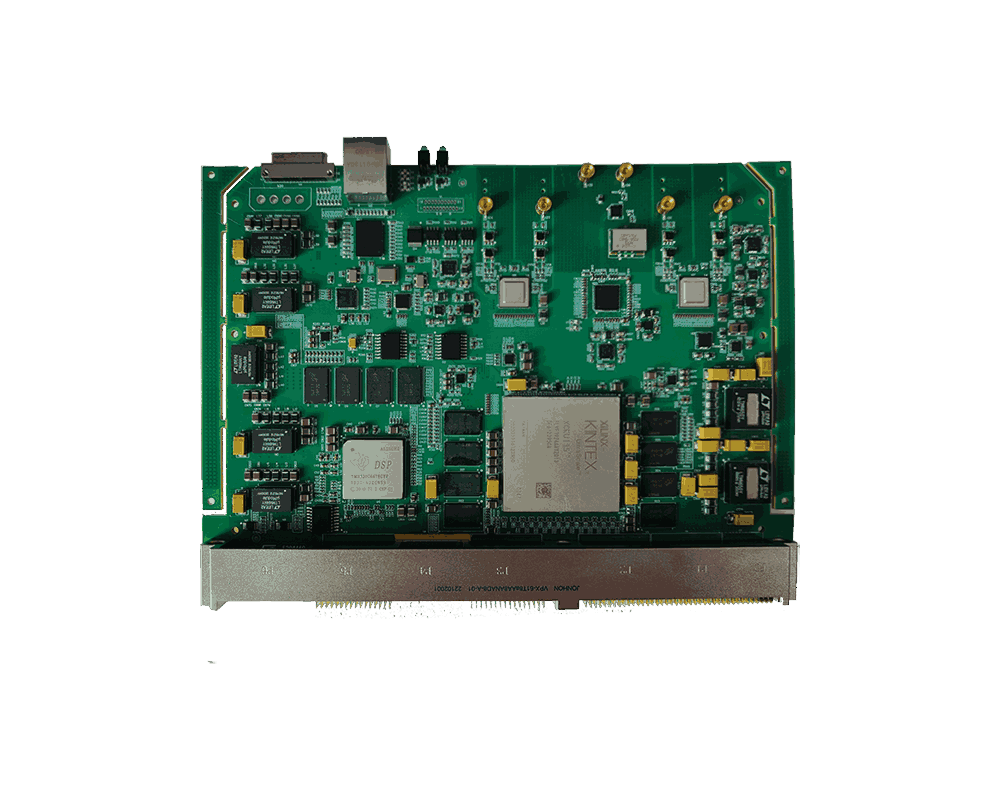

3.2.1 DSP+FPGA调制信号发生器

在统一的硬件平台上,实现多种调制信号,需采用软件无线电设计思想。调制信号发生器采用DSP+FPGA+DAC架构,具有很强的通用性和灵活性,DSP通过USB接口接收用户设置的调制方式、调制码速率等参数,并解析工控机上层软件指令,配置FPGA内滤波器和时钟,FPGA根据配置产生相应的调制映射、滤波器、数字载波等,终生成数字中频信号,再通过DAC,输出模拟中频信号。原理框图如图3所示。

图3

3.2.2 射频发射前端

射频发射模块采用二次上变频设计完成对中频信号的变频处理和发射。发射模块主要由中频低通滤波器、上变频器、放大器、大动态/小步进功率衰减器、检波器组成,见图4。

图4

其中,300MHz点频源采用直接倍频、滤波方法产生,将系统时钟100MHz通过宽带放大器饱和放大产生,100MHz的N次谐波,再通过滤波器取出3次谐波300MHz。

2475MHz点频源采用锁相环PE3336实现,实现原理框图如图5所示。

图5

3.3接收子系统设计

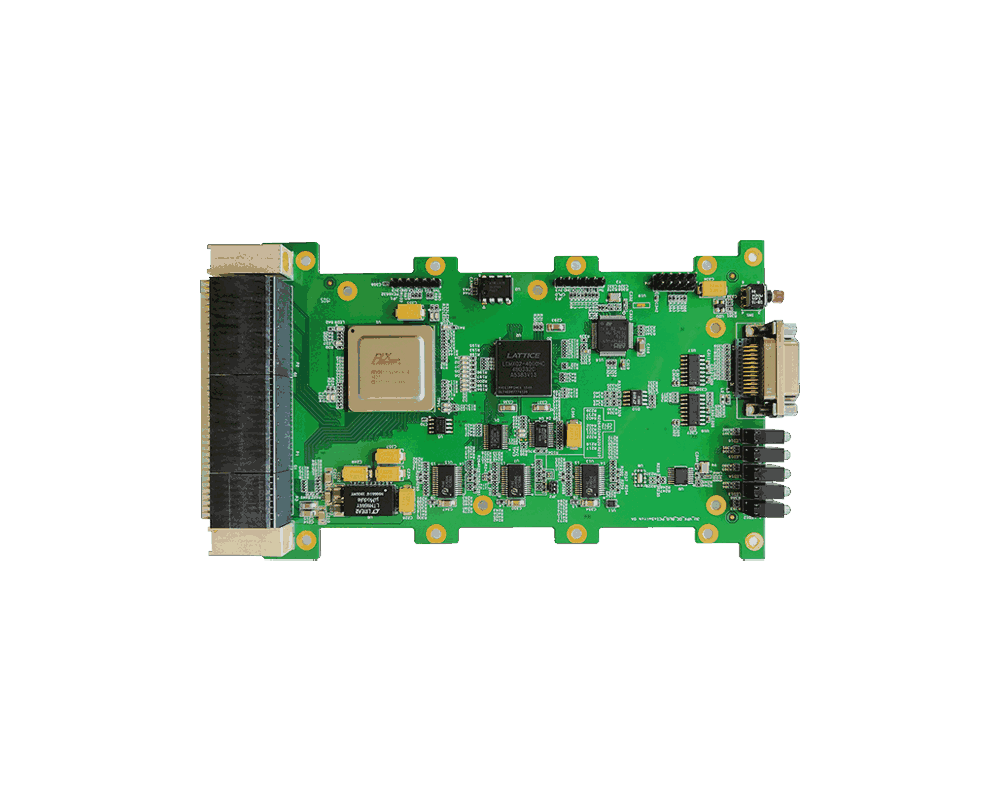

3.3.1 DSP+FPGA数字解调器

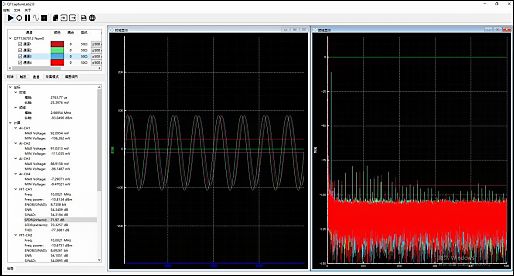

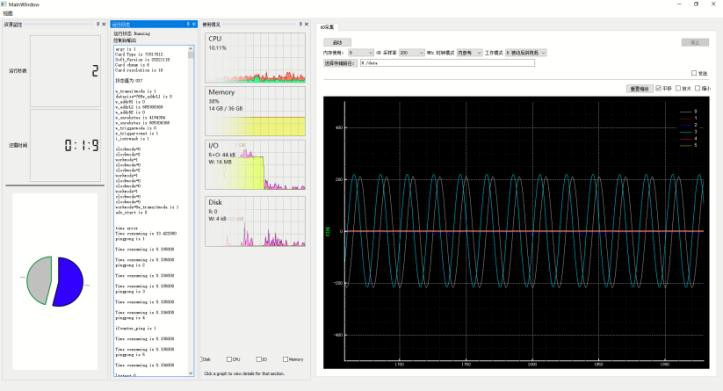

为了实现多种调制制式的解调,采用ADC+FPGA+DSP的硬件架构,ADC以带通过采样方式采集中频信号,采集后数字中频信号在FPGA内实现抽取、滤波、载波同步、码同步数字信号处理,处理后在DSP内实现解调、解交织、解码,终码数据通过USB上传至工控机,进行比对分析、星座图显示等。原理框图如图6所示。

图6

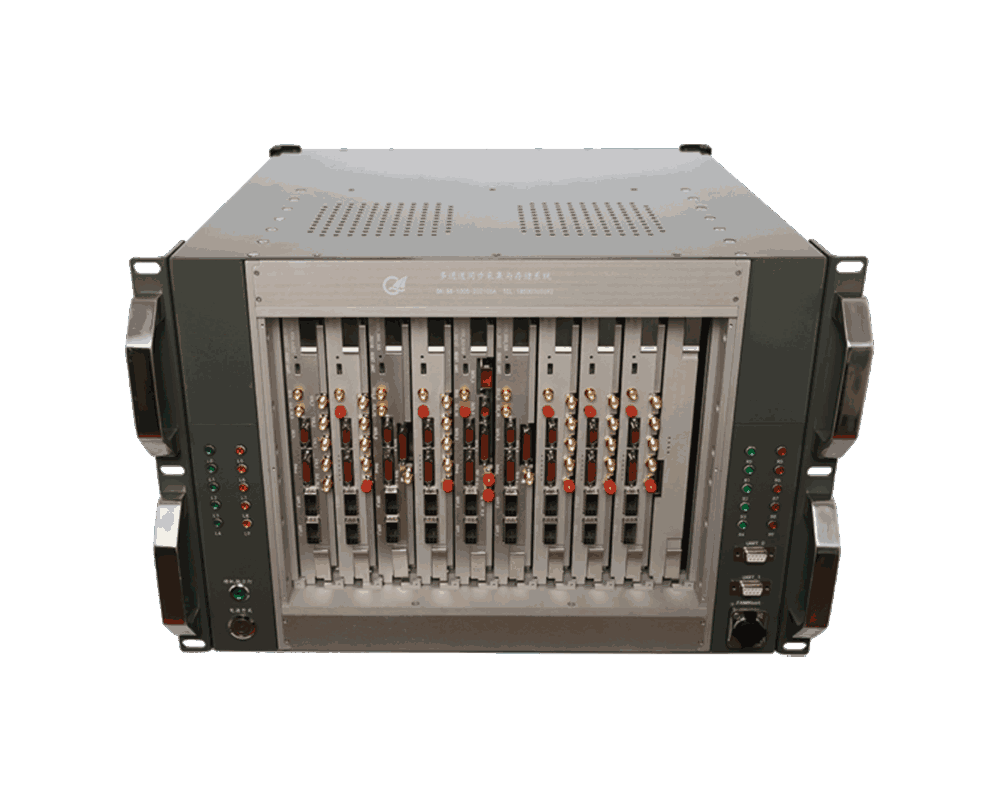

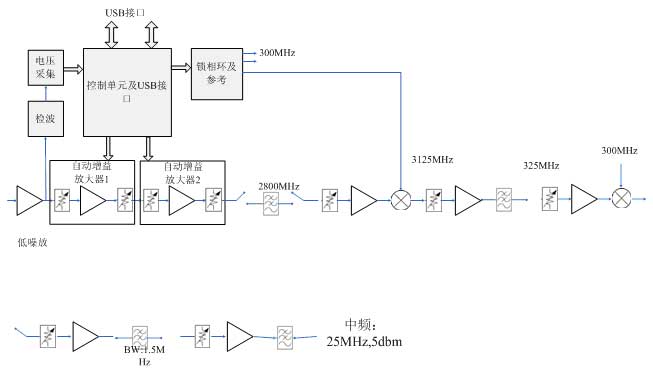

3.3.2 射频接收前端及控制

射频接收前端主要由低噪声放大器、镜像滤波器、自动增益放大器、射频检波电路、开关、混频器、本振源等电路组成。射频接收前端原理框图如图7所示。射频接收前端低噪声放大器增加射频接收前端灵敏度,功率检波电路测量低噪声放大器输出的射频信号功率,控制自动增益放大器满足射频接收前端-90—10dbm线性功率动态范围的要求,并使得射频输入电平处于混频器、中频放大器及检波器的佳量程范围。

图7

3125MHz点频源采用锁相环ADF4350实现。

-

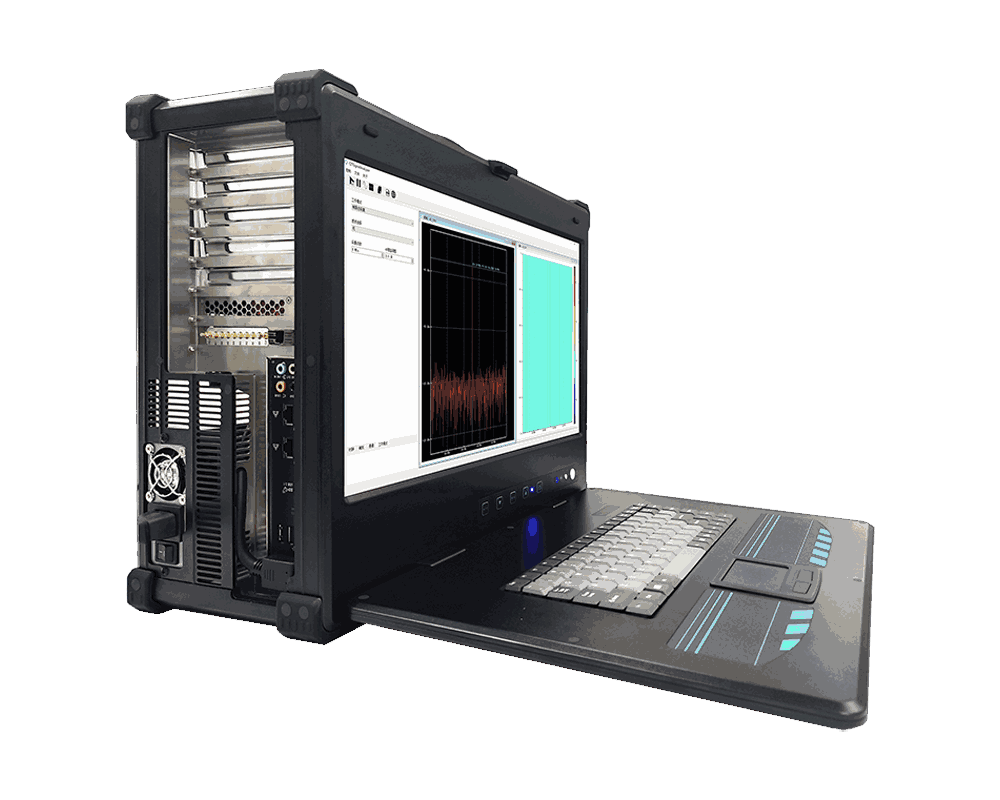

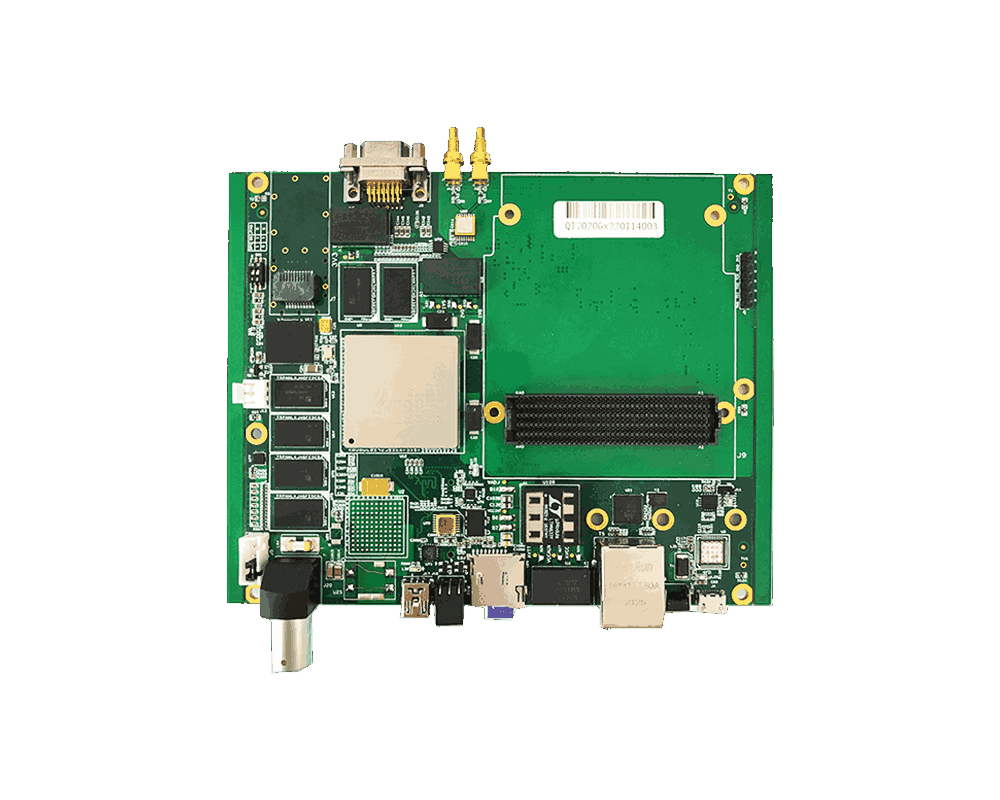

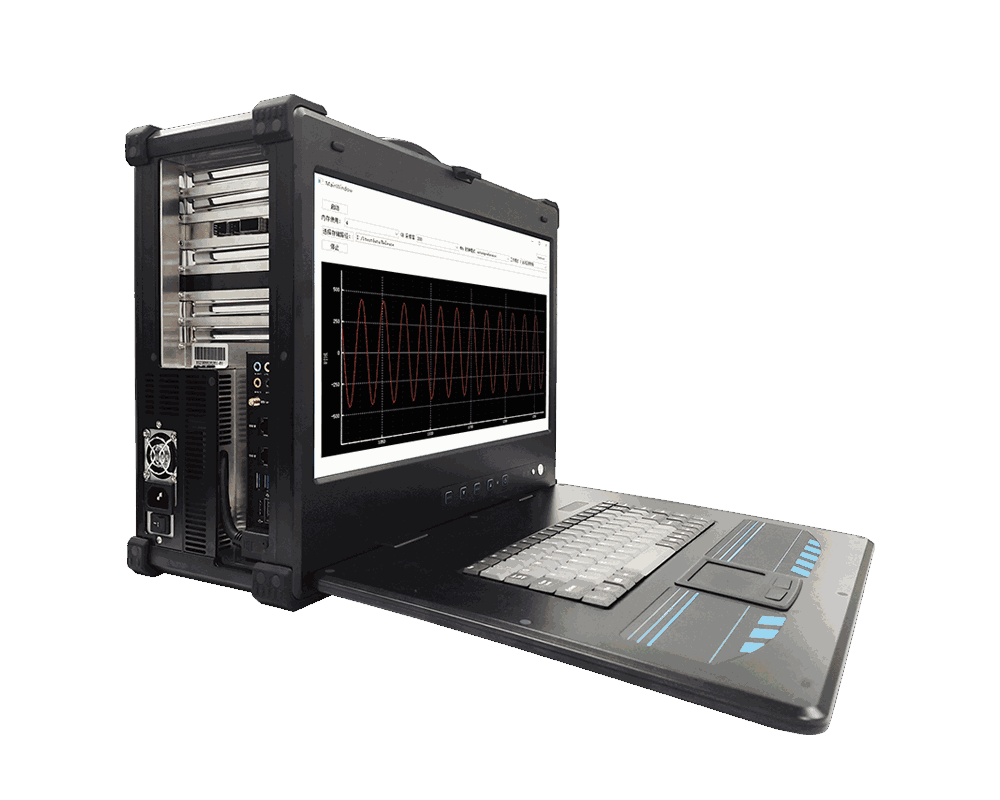

瞬态记录仪

基于以太网 高达120MS/s的采样频率 高达16位分辨率 满量程精度0.03%

-

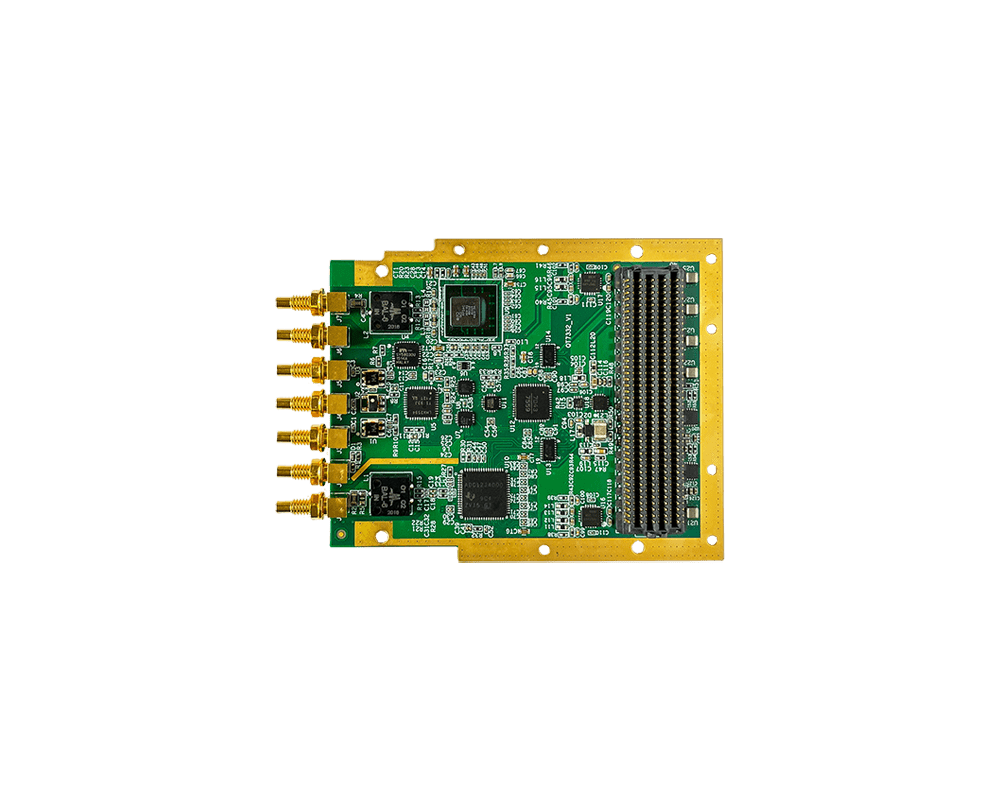

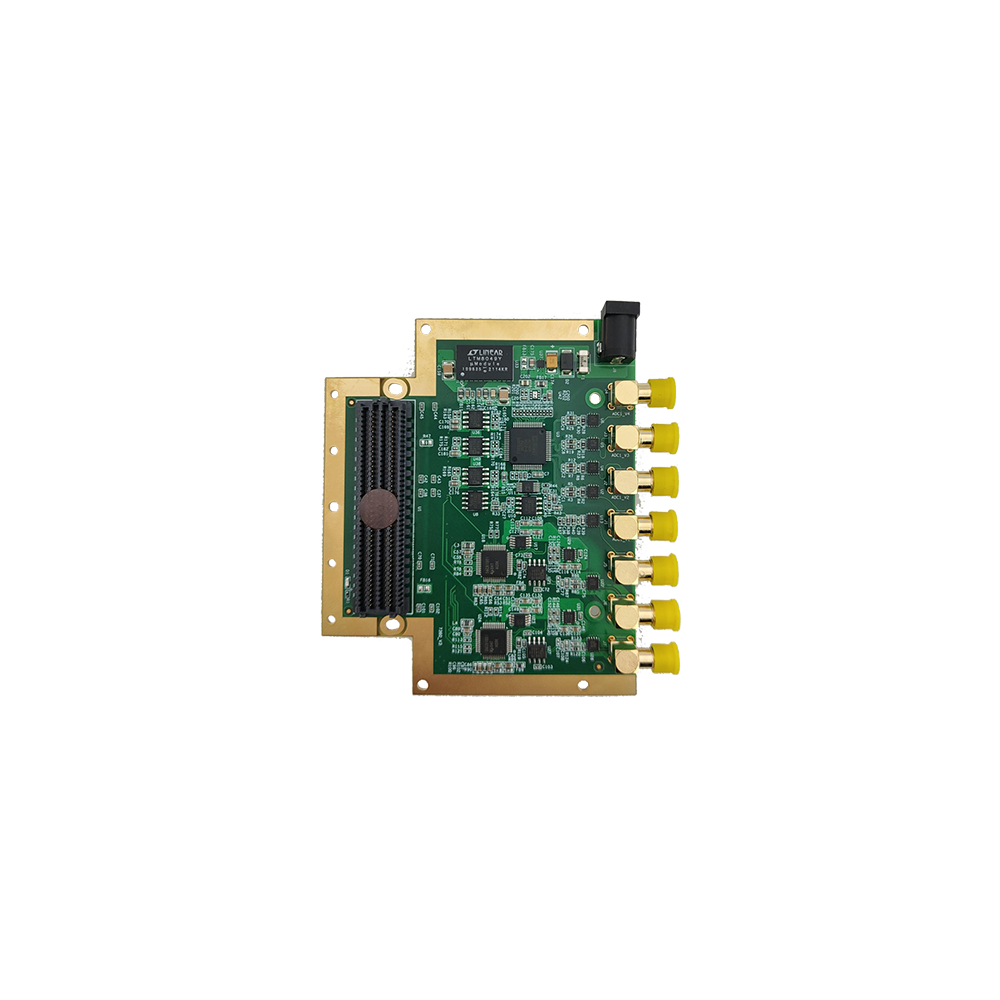

ADQ7WB-PXIe宽带中频采集卡

♦2通道,12bit分辨率,5GSPS采样率

♦6.5GHz模拟输入带宽及4GB板载内存

♦适用射频监控和记录等应用

-

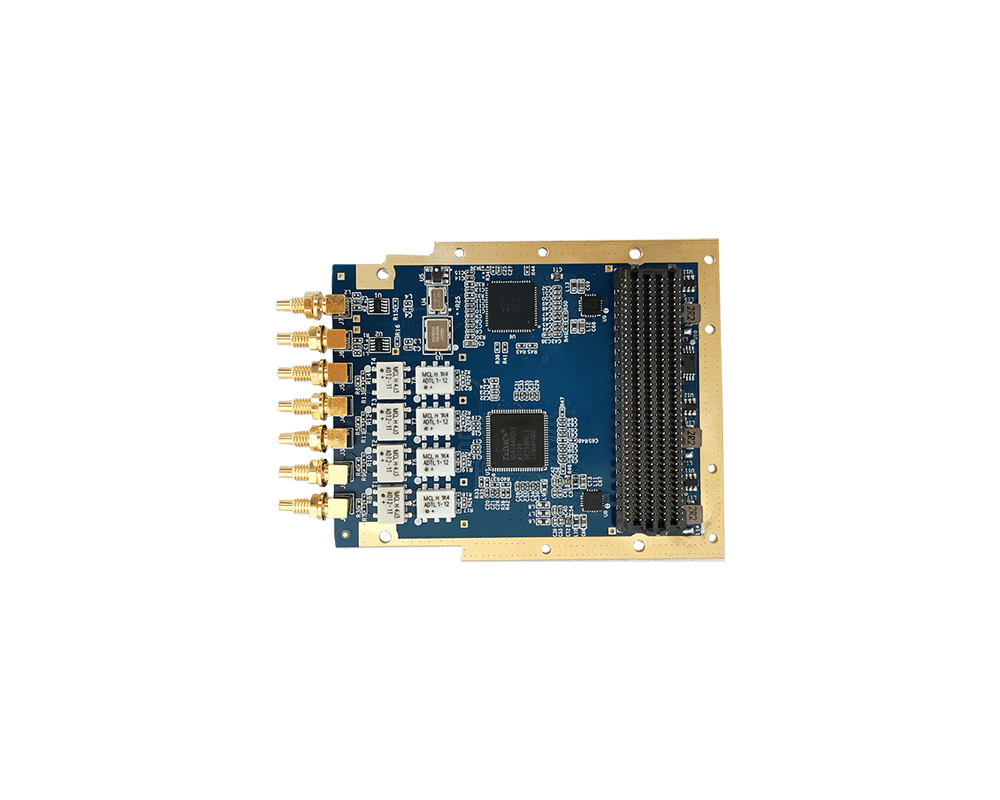

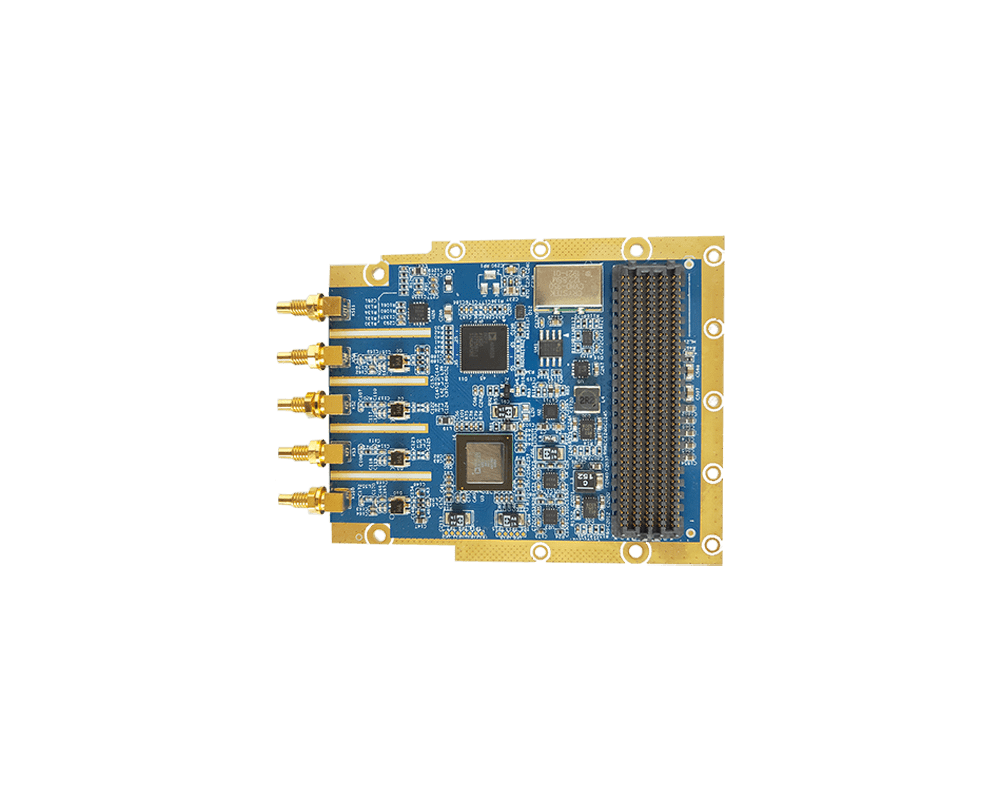

QT12125-宽带中频采集卡

2路通道 位数:12bit 采样率:5.2GS/s双通道

-

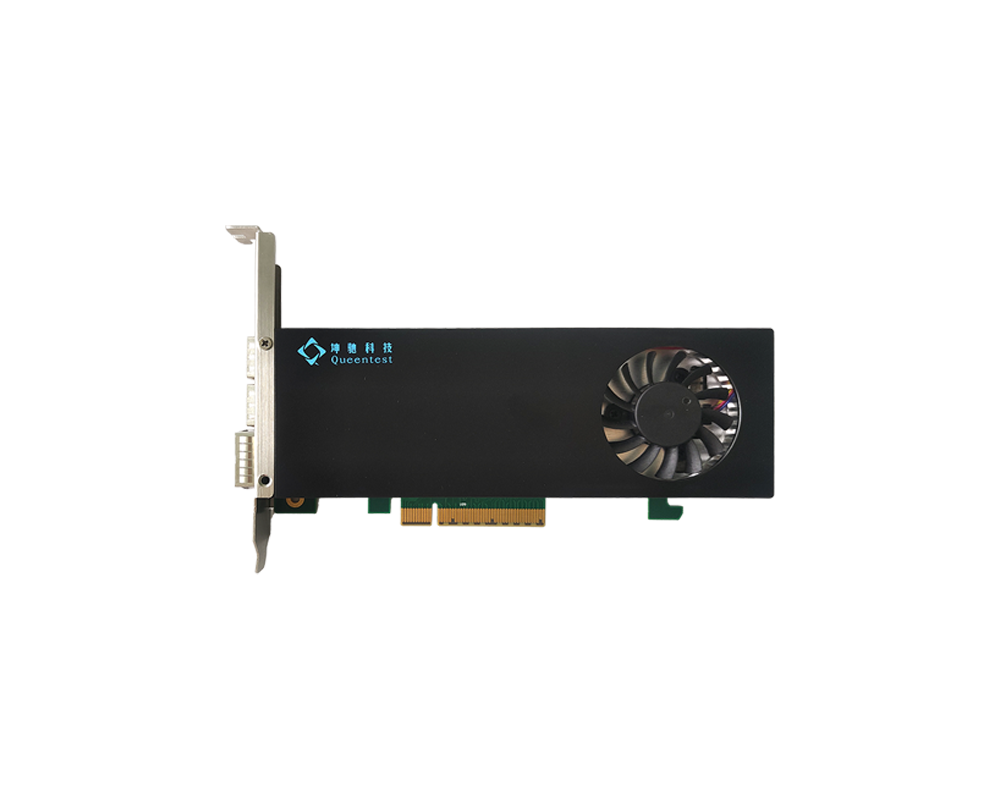

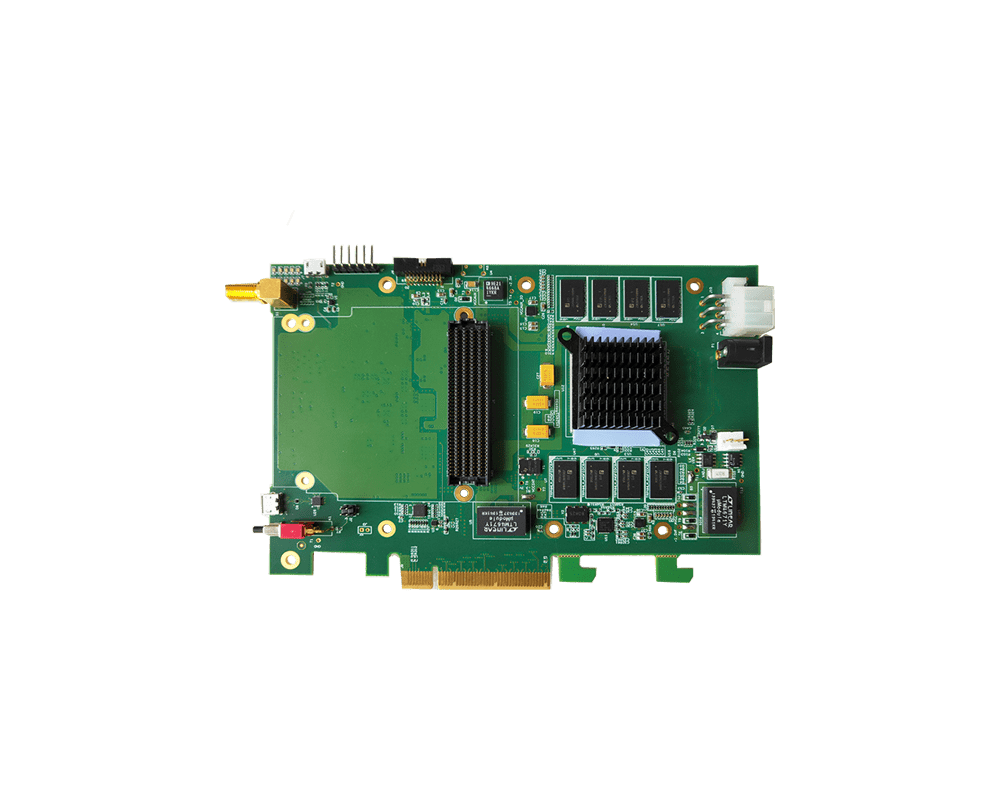

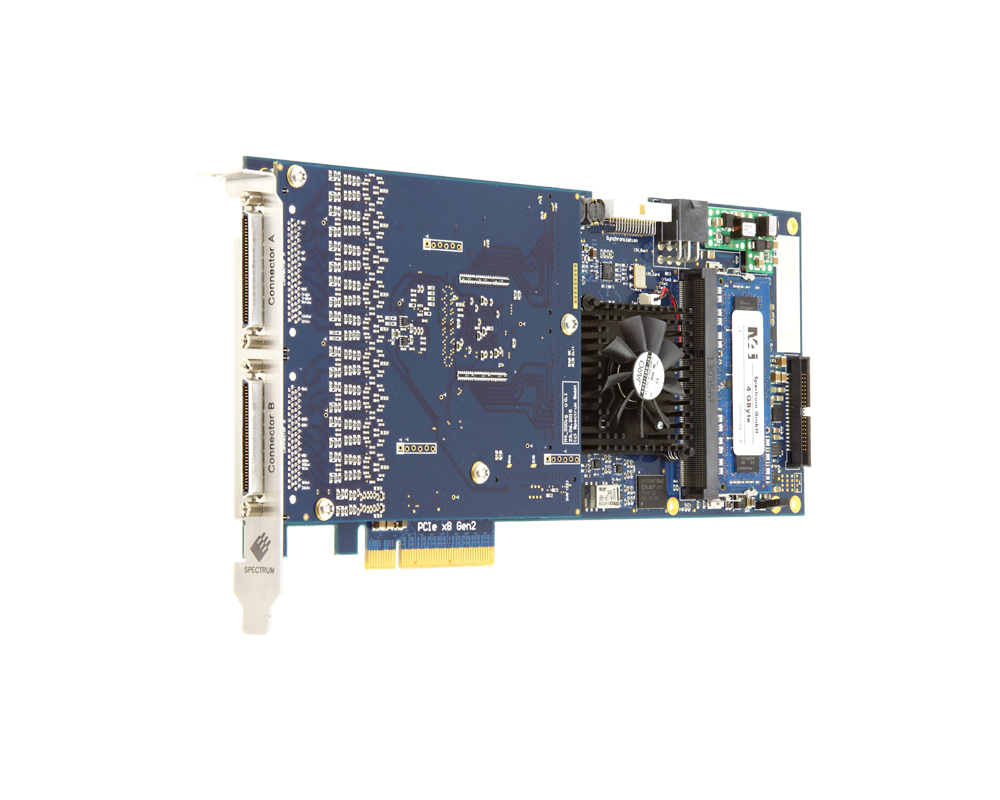

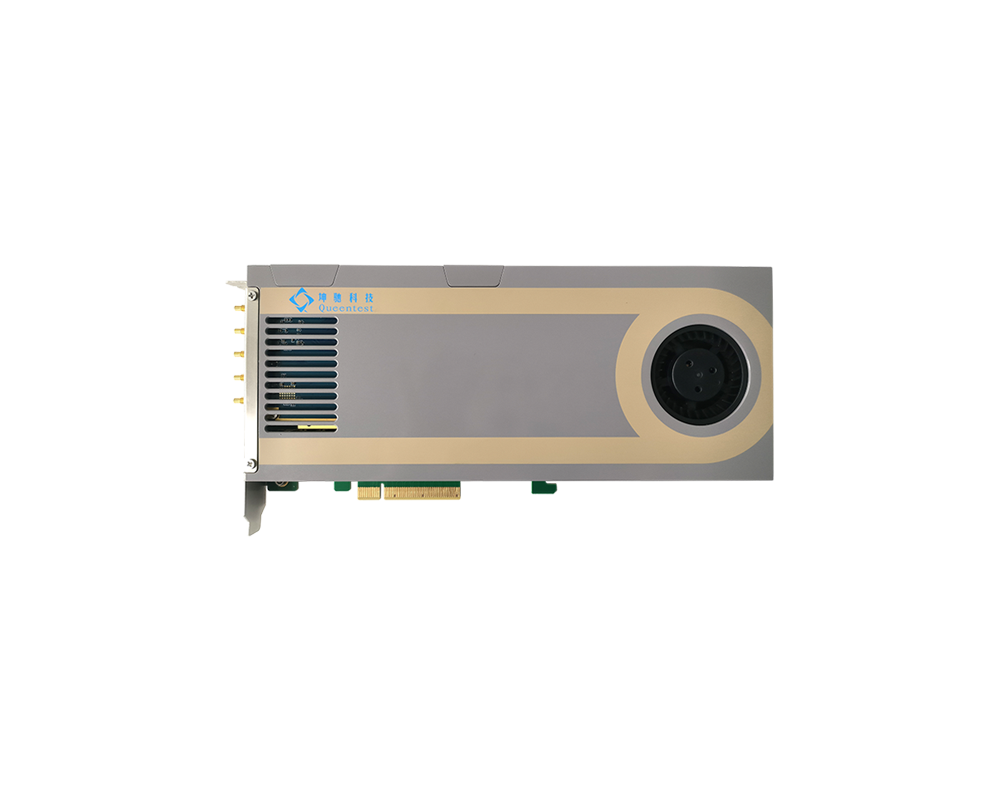

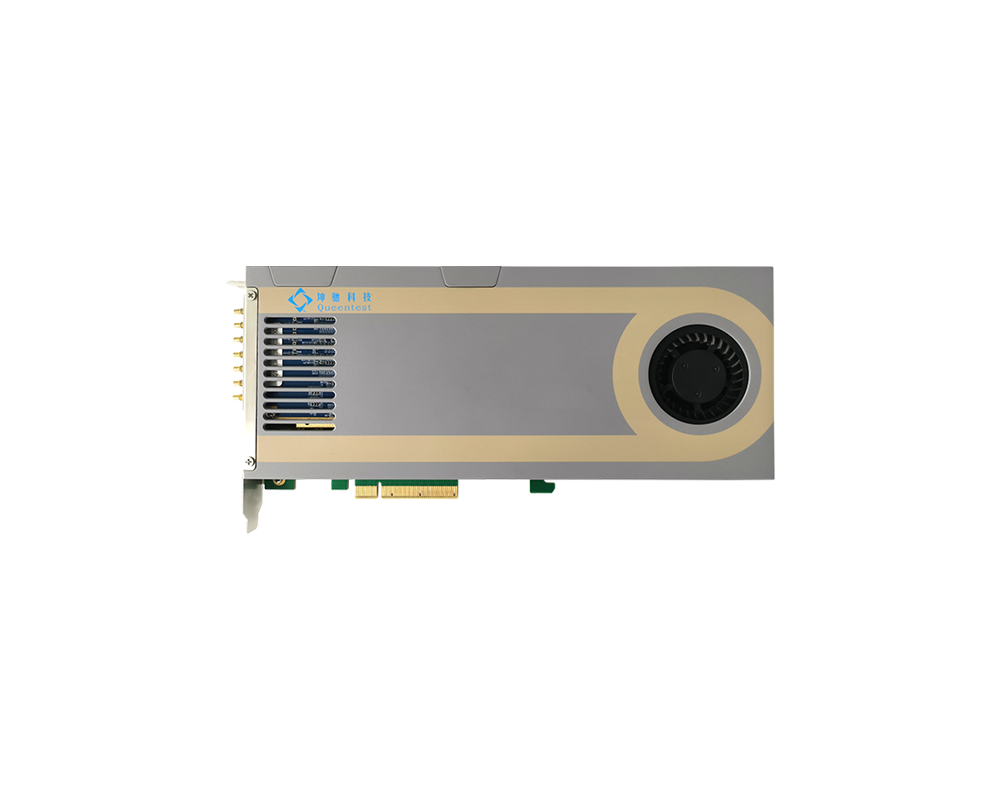

QT12136-宽带中频采集卡

坤驰科技自主研发的QT12136是一款支持宽带RF/IF信号输入的高速数据采集卡。这使QT12136成为雷达阵列信号处理,软件无线电,宽带通信,数采,通信测试设备应用的理想工具。QT12136提供快速的PCIExpress3.0 x8数据传输接口,尤其适合于OEM应用。